# **Quasi-TEM Model for Coplanar Waveguide on Silicon**

Dylan F. Williams and Michael D. Janezic National Institute of Standards and Technology 325 Broadway, Boulder, CO 80303 Ph: (303)497-3138 Fax: (303)497-3122 E-mail: dylan@boulder.nist.gov

Andrew R. K. Ralston and R. Scott List Texas Instruments Incorporated 13536 N. Central Expressway, Dallas, TX 75243 Ph: (972) 927-3817 Fax: (972) 995-2770 E-mail: ralston@spdc.ti.com

Abstract- This paper compares a simple quasi-TEM model for coplanar waveguide fabricated on moderately doped silicon substrates to measurement. While the coplanar waveguide currents and magnetic fields are unaffected by the substrate, a simple capacitive model can accurately account for the effects of the substrate.

### INTRODUCTION

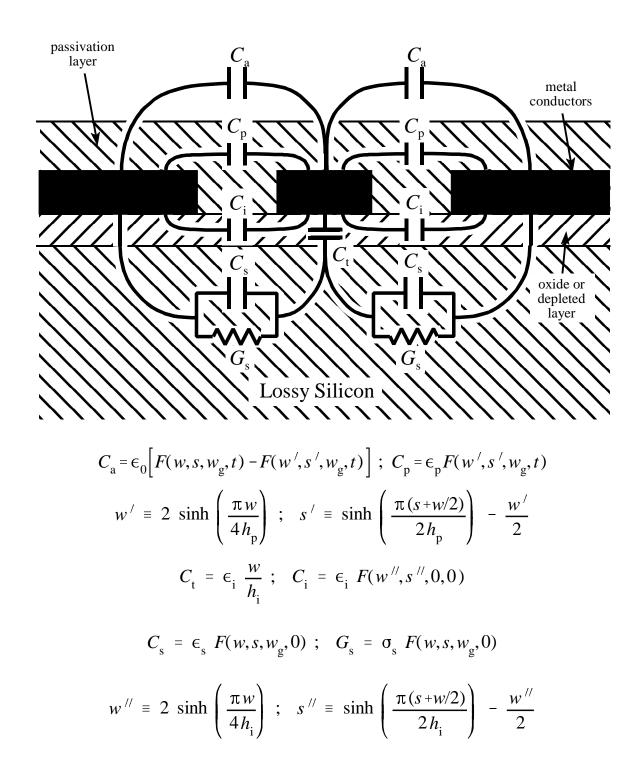

We apply the calibration comparison method [1], [2] to directly measure the resistance R, inductance L, capacitance C, and conductance G per unit length of coplanar waveguide (CPW) fabricated on silicon substrates and show that the model of Fig. 1 accurately determines C and G.

Kwong, et al. [3], Seguinot, et al. [4], and Ko, et al. [5] have proposed closed-form expressions for analyzing CPW on silicon substrates. However the analysis of [3] requires some finite-difference calculations, the models of [3] and [4] neglect the capacitance through the silicon substrate, and Williams, et al. [6] point out some difficulties in the analysis of [5]. Here we compare to measurement the model of Fig. 1, which is based on closed-form expressions from [3], [5], [7], and [8] and accounts for substrate capacitance, conductance, and fringing fields.

## MEASUREMENT PROCEDURE

Reference [2] showed how to use the calibration comparison method [1] to accurately determine the inductance *L*, capacitance *C*, resistance *R*, and conductance *G* per unit length of printed transmission lines. A multiline thru-reflect-line (TRL) calibration [9] measures the line's propagation constant  $\gamma$  directly. A comparison of this calibration, whose reference impedance is equal to the characteristic impedance  $Z_0$  of the transmission line [10], to a multiline TRL reference calibration with reference impedance correction [11] determines  $Z_0$ . Then *L*, *C*, *R*, and *G* are found from  $R+j\omega L \equiv \gamma Z_0$  and  $G+j\omega C \equiv \gamma/Z_0$ .

In this work we apply this method to CPW fabricated on moderately doped silicon substrates using CPW reference lines fabricated on semi-insulating gallium arsenide. These reference lines had a metal thickness *t* of 0.5 µm and center conductor width *w* of 73 µm separated from two ground planes of width  $w_g=250 \text{ µm}$  by gaps of width *s*=49 µm.

## INDUCTANCE AND RESISTANCE

We first investigated the *L*, *R*, *C*, and *G* per unit length of the three CPWs of [2] fabricated directly on silicon substrates. These CPW conductors were formed by evaporating a thin titanium adhesion layer followed by approximately 0.5  $\mu$ m of gold directly on three different silicon substrates. To assure the maximum measurement accuracy, [2] used the same metal geometries and metal thickness as the reference wafer.

Figure 2 of [2] compared L and R for these CPWs to that of the CPW fabricated on the semi-insulating gallium arsenide reference wafer and showed that R and L were insensitive to changes in the substrate. This indicates that the magnetic fields in the CPW are not affected by these moderately doped substrates: the currents are still confined to the metals.

## CAPACITANCE AND CONDUCTANCE

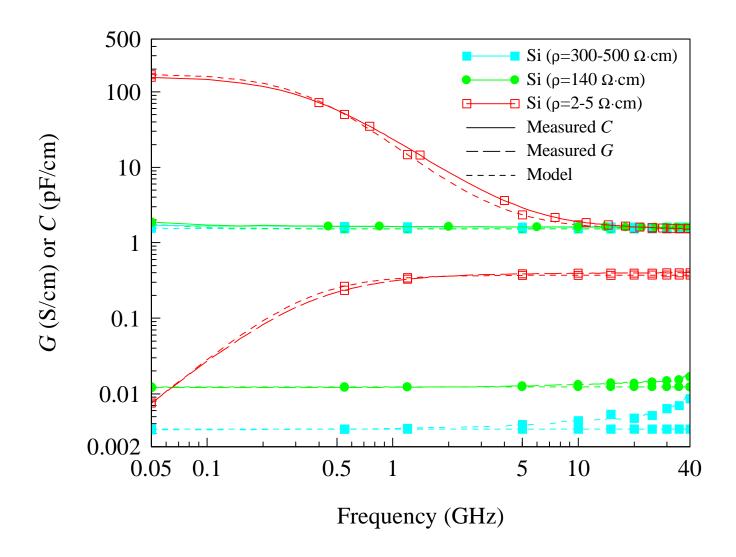

Figure 2 shows the capacitance C and conductance G per unit length of the CPW measured in [2]: this figure shows that C and G are changed by the substrate parameters. It also compares the measurements of C and

Publication of the National Institute of Standards and Technology, not subject to copyright. Reprinted from 1997 IEEE 6<sup>th</sup> Topical Meeting on Electrical Performance of Electronic Packaging, pp. 225-228, Oct. 27-29, 1997.

G to the results of the simple quasi-TEM model of Fig. 1 and shows good agreement. This model attributes C and Gto the properties of the silicon substrate and the thickness and dielectric constant of the native oxides or depleted regions between the metals and the silicon substrate: the models of [3] and [4], which neglect the substrate capacitance, underestimate the measured capacitances significantly. The close agreement of this simple quasi-TEM model with the measurements also indicates that the interaction of the electric fields with the lossy silicon substrate has not given rise to any significant non-TEM phenomena.

We determined all of the parameters of the closed form model from direct measurement, approximate manufactures specifications, and material parameters found in the literature. On the 300-500  $\Omega \cdot \text{cm}$  and the 140  $\Omega \cdot \text{cm}$  substrates we left a native oxide on the silicon surface before metal deposition. Here we set  $\rho_s=1/\sigma_s=400$  $\Omega \cdot \text{cm}$  and 110  $\Omega \cdot \text{cm}$ , consistent with the approximate specifications from the manufacturer,  $\epsilon_i=3.9\epsilon_0$  and  $h_i$ equal to 0.005 µm and 0.0037 µm, the measured oxide thicknesses. For the CPW on the 2-5  $\Omega \cdot \text{cm}$  p-type substrate we removed the native oxide. Here we set  $\rho_s=1/\sigma_s=3.6 \Omega \cdot \text{cm}$  and  $\epsilon_i=11.7\epsilon_0$  and  $h_i = 0.44 \mu \text{m}$ , the calculated depletion depth at the metal-semiconductor interface.

## **CPW WITH THICK PASSIVATION**

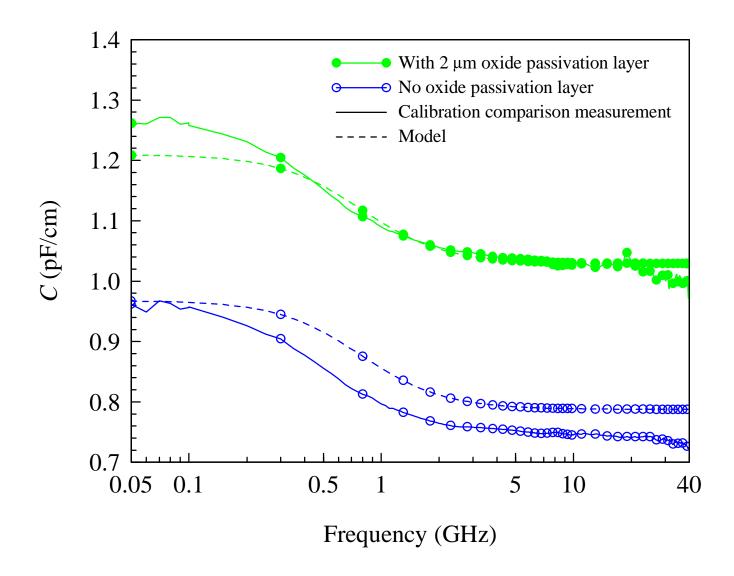

We also fabricated CPWs with  $w = s = 10 \mu m$ , 5  $\mu m$ , and 2  $\mu m$  on a thick oxide layer grown on 135  $\Omega$ ·cm silicon substrate. These lines had a metal thickness *t* of 2  $\mu m$ ; we assumed that the relative dielectric constant of the 6  $\mu m$  thick oxide layer and 4  $\mu m$  thick passivation layer was 3.9, reasonable for these SiO<sub>2</sub> layers. Figure 3 shows that the *C* and *G* predicted by the model for  $w = s = 10 \mu m$ with and without the thick passivation layer compare well to the measured values; agreement for the other cases was similar.

## CONCLUSION

We studied a number of CPWs fabricated on silicon substrates. Neither R nor L was affected by the substrate, perhaps because the substrate conductivity was not too high [3]. This result indicates that the currents and the magnetic field solutions correspond to those of a CPW on a low-loss dielectric. Although C and G were shown to depend on the substrate parameters, they were well described by a simple capacitive quasi-TEM model: no non-TEM phenomena were required in the description. The model investigated here accounts for substrate capacitance and, unlike the models of [3] and [4], estimates the measured CPW capacitance accurately; its ability to account for the capacitance of the passivation layer suggests that it could be used to estimate its dielectric constant.

## **ACKNOWLEDGMENTS**

The authors thank Nita Morgan for test-structure fabrication and David Walker for his explanations of the physics of the metal-semiconductor interface.

## REFERENCES

[1] D. F. Williams, R. B. Marks, and A. Davidson, "Comparison of on-wafer calibrations," *38<sup>th</sup> ARFTG Conference Digest*, pp. 68-81, Dec. 1991.

[2] D. F. Williams and R. B. Marks, "Accurate transmission line characterization," *IEEE Microwave Guided Wave Lett.*, pp. 247-249, Aug. 1993.

[3] Y. R. Kwon, V. M. Hietala, and K. S. Champlin, "Quasi-TEM analysis of 'slow-wave' mode propagation on coplanar microstructure MIS transmission lines," *IEEE Trans. Microwave Theory Tech.*, pp. 545-551, June 1987.

[4] C. Seguinot, P. Kennis, and P. Pribetich, "Desktop computer appraisal of potential slow-wave propagation characteristics for Schottky coplanar lines," *Electron. Lett.*, pp. 1065-1067, Dec. 1983.

[5] J. Ko, B. Kim, and K. Lee, "Simple modeling of coplanar waveguide on thick dielectric over lossy substrate," *IEEE Trans. Electron Devices*, vol. 44, pp. 856-861, May 1997.

[6] D. F. Williams, J. Ko, B. Kim, and K. Lee, "Comments on 'Simple modeling of coplanar waveguide on thick dielectric over lossy substrate'," submitted to *IEEE Trans. Electron Devices*.

[7] E. Chen and S. Y. Chou, "Characteristics of coplanar transmission lines on multilayer substrates: modeling and experiments," *IEEE Trans. Microwave Theory and Tech.*, pp. 939-945, June 1997.

[8] W. Heinrich, "Quasi-TEM description of MMIC coplanar lines including conductor-loss effects," *IEEE Trans. Microwave Theory Tech.*, pp. 45-52, Jan. 1993.

[9] R. B. Marks, "A Multiline Method of Network Analyzer Calibration," *IEEE Trans. Microwave Theory Tech.*, pp. 1205-1215, July 1991.

[10] R. B. Marks and D. F. Williams, "A general waveguide circuit theory," *J. Res. Natl. Inst. Stand. Technol.*, pp. 533-561, Sept.-Oct. 1992.

[11] R. B. Marks and D. F. Williams, "Characteristic Impedance Determination using Propagation Constant Measurement," *IEEE Microwave Guided Wave Lett.*, pp. 141-143, June 1991.

Fig. 1. The capacitive model used in this work. Here *w* is the center conductor width, *s* the gap width,  $w_g$  the ground-plane width, *t* the metal thickness,  $h_i$  and  $\epsilon_i$  the thickness and permittivity of the lower oxide or depleted layer, and  $h_p$  and  $\epsilon_p$  the thickness and permittivity of the passivation layer. The expression for  $F(w,s,w_g,t)$  is given in (1) of [8]. The expressions for *w*' and *s*' are taken from [7].

Fig. 2. The modeled and measured *C* and *G* for three CPWs fabricated directly on silicon. (Measurements from [2].)  $c:e_z_det_cir_new_log_gc.plt$

Fig. 3. The modeled and measured C of CPW with and without a thick  $SiO_2$  passivation layer. c:\htb386\CPWmodel\Janezic\_TI\sio50\_c.plt