# Silicon Carbide Power MOSFET Model and Parameter Extraction Sequence

Ty McNutt<sup>1</sup>, Allen Hefner<sup>2</sup>, Alan Mantooth<sup>1</sup>, David Berning<sup>2</sup>, Sei-Hyung Ryu<sup>3</sup>

<sup>1</sup>University of Arkansas **BEC 3217** Fayetteville, AR 72701

<sup>2</sup>National Institute of Standards and Technology\* Semiconductor Electronics Division Gaithersburg, MD 20899-8120

<sup>3</sup> CREE Research 4600 Silicon Drive Durham, NC 27703

Abstract- A compact circuit simulator model is used to describe the performance of a 2 kV, 5 A 4-H silicon carbide (SiC) power DiMOSFET and to perform a detailed comparison with the performance of a widely used 400 V, 5 A silicon (Si) power MOSFET. The model's channel current expressions are unique in that they include the channel regions at the corners of the square or hexagonal cells that turn on at lower gate voltages and the enhanced linear region transconductance due to diffusion in the nonuniformly doped channel. It is shown that the model accurately describes the static and dynamic performance of both the Si and SiC devices and that the diffusion-enhanced channel conductance is essential to describe the SiC DiMOSFET on-state characteristics. The detailed device comparisons reveal that both the on-state performance and switching performance at 25 °C are similar between the 400 V Si and 2 kV SiC MOSFETs, with the exception that the SiC device requires twice the gate drive voltage. The main difference between the devices is that the SiC has a five times higher voltage rating. At higher temperatures (above 100 °C), the Si device has a severe reduction in conduction capability, whereas the SiC onresistance is only minimally affected.

## NOMENCLATURE

- Device active area  $(cm^2)$ A Drain-body junction area  $(cm^2)$ Ads  $\begin{array}{c} A_{gd} \\ C_{dsj} \\ C_{gd} \\ C_{gi} \\ C_{gdj} \\ C_{gs} \\ C_{oxd} \end{array}$ Gate-drain overlap area  $(cm^2)$ Drain-source junction capacitance (F) Gate-drain capacitance (F) Gate-inversion layer capacitance (F) Gate-drain junction capacitance (F)

- Gate-source capacitance (F)

- Gate-drain overlap oxide capacitance (F)

- dVπ Low current threshold voltage differential (V)

- Semiconductor dielectric constant (F/cm) Esemi

- Fraction depletion charge at gate-drain overlap edge Fxjbe Fraction depletion charge at gate-drain overlap Fxjbm

- middle

- $I_{mos}$ MOSFET channel current (A)

- Low current region component of  $I_{mos}$  (A) Imosl

- High current region component of  $I_{mos}$  (A) Imosh

- Boltzmann's constant (J/K) k

- Linear region transconductance factor

- $K_f$ К<sub>л</sub> Low current region transconductance factor

- Κ<sub>p</sub> Saturation region transconductance  $(A/V^2)$

- K<sub>psal</sub> Extracted saturation region transconductance  $(K_n)$ ,  $(A/V^2)$

- K<sub>plin</sub> Extracted linear region transconductance  $(K_{kn})$ ,  $(A/V^2)$

- Bulk electron mobility  $(cm^2/V \cdot s)$  $\mu_n$

- Base dopant density (cm<sup>-3</sup>) Nb

- Intrinsic carrier concentration (cm<sup>-3</sup>)  $n_i$

- $P_{vf}$ Pinch-off voltage factor

- Fundamental electronic charge (C) q

- Epitaxial layer resistance ( $\Omega$ )  $R_b$

- Series drain resistance ( $\Omega$ ) R<sub>s</sub>

- Т Chip surface temperature (K)

- θ Transverse electric field parameter  $(V^{-1})$

- $V_{bi}$ Built-in junction potential (V)

- $V_{bigd}$ Built-in potential of gate-drain overlap region (V)

- Drain-source terminal voltage (V)  $V_{dds}$

- MOSFET channel voltage (V)  $V_{ds}$

- Gate-source voltage (V) Vgs

- Gate-drain overlap depletion threshold (V) V<sub>Td</sub>

- Gate drain overlap inversion threshold voltage (V) V<sub>Tdi</sub>

- $V_{Tdiedge}$  $V_{Tdi}$  at body edge of gate-drain overlap (V)

- $V_{Tl}$ Low current MOSFET channel threshold voltage (V)

- High current MOSFET channel threshold voltage  $V_{Th}$ (V)

- W Quasineutral drift region width (cm)

- W<sub>b</sub> Metallurgical drift region width (cm)

- $W_{dsj}$ Drain-body depletion width (cm)

- y Pinch-off voltage exponent

# **I. INTRODUCTION**

Recently, silicon carbide (SiC) power devices have begun to emerge with performance that is superior to that of silicon (Si) power devices. For a given blocking voltage, SiC minority carrier conductivity modulated devices, such as a

<sup>\*</sup> Contribution of the National Institute of Standards and Technology is not subject to copyright.

PiN diode, are expected to show an improvement in switching speed by a factor of 100 as compared to Si, while majority carrier SiC devices are expected to show a factor of 100 advantage in resistance compared to Si [1]. Prototype devices have already demonstrated improvements over Si technology for devices of various current and voltage ratings, and SiC Schottky diodes have been made commercially available.

In order for circuit designers to fully utilize the advantages of the new SiC power device technologies, compact models are needed in circuit and system simulation tools. In [2] a compact SiC power diode model for use in the Saber<sup>®</sup> circuit simulator [3] was described and an extraction sequence for this model was developed in [4]. The comprehensive SiC diode model is capable of accurately describing the static, dynamic, and electrothermal performance of SiC Schottky, Junction-Barrier Schottky, and PiN diodes. It is anticipated that SiC power device models with extracted parameter sets will be provided in circuit simulator libraries and will be used to provide insight into the performance advantages of SiC power diodes.

The purpose of this paper is to develop a new model and parameter extraction sequence for SiC power MOSFETs. The model is used to describe the performance of a 2 kV, 5 A 4H-SiC Double implanted MOSFET (DiMOSFET) and to perform a detailed comparison with the performance of a widely used 400 V, 5 A Si Vertical Double-Diffused power MOSFET (VDMOSFET). The model is based upon the latest version of the power MOSFET model utilized in the Hefner IGBT model [5], where the parameters of both the Si and SiC MOSFETs can be extracted using the IGBT Model Parameter ExtrACtion Tools (IMPACT) software [6]. Both the model and extraction tools are enhanced and extended for the purpose of this work to include the temperature dependent material properties of SiC materials as well as the additional device physics required to describe the DiMOSFET structure.

# **II. SILICON CARBIDE DIMOSFET**

SiC power MOSFETs are expected to have advantages over existing Si technology similar to that of the above mentioned SiC diodes. With a high critical electric field (~ 2 MV/cm), reasonable bulk electron mobility (~ 800 cm<sup>2</sup>/V·s), and high saturation velocity (~  $2 \cdot 10^7$  cm/s) [7,8], 4H-SiC is attractive for implementation of high voltage, high-speed power devices. These physical properties are suitable for making high performance 4H-SiC unipolar devices capable of blocking 1 kV - 3 kV. For the same range of blocking voltages, typical silicon power devices utilize conductivity modulation in the drift layer to reduce the forward drop, resulting in reduced switching speeds.

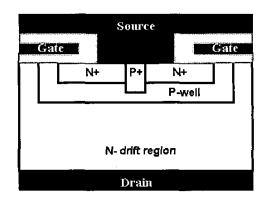

Fig. 1 shows the simplified cross section of the unit cell structure of a recently introduced 2 kV, 5 A SiC DiMOSFET that has fast switching performance [9]. The structure of the DiMOSFET is similar to that of the VDMOSFET used for Si power MOSFETs, in that the p-well and  $n^+$  source regions typical of the VDMOSFET structure still exist in the

Fig. 1. Cell structure for a 5 A, 2 kV SiC DiMOSFET.

DiMOSFET structure. The main difference between the two structures is that the DiMOSFET p-well and  $n^+$  source regions are much more shallow than those of a Si VDMOSFET due to the much lower impurity diffusion coefficients inherent in SiC.

For the fabricated devices shown in Fig. 1, the MOSFET channel length is 1.5  $\mu$ m and is defined by the p-well and n<sup>+</sup> implants. The cell pitch is 16  $\mu$ m, and the packing density of the gate periphery is 1250 cm/cm<sup>2</sup>. A 2.5  $\cdot$  10<sup>15</sup> cm<sup>-3</sup> doped, 20  $\mu$ m thick n-type drift layer is used in the device. In the onstate region of operation, electrons flow laterally from the n<sup>+</sup> source through the MOSFET channel formed in the implanted p-well and then vertically between adjacent cells and through the lightly-doped drift layer to the drain contact. For a 2 kV Si MOSFET, the drift layer resistance dominates the on-resistance of the device, whereas the specific on-resistance is dominated by the channel resistance for the SiC DiMOSFET structure [9].

The fabrication of the DiMOSFET begins with an n-type SiC wafer with a  $2.5 \cdot 10^{15}$  cm<sup>-3</sup> doped, 20 µm thick epitaxial layer. The p-wells are formed by aluminum implantation followed by a heavy-dose nitrogen implant for the  $\boldsymbol{n}^{\scriptscriptstyle +}$  source regions. A heavy-dose of aluminum is implanted to form the  $p^{\dagger}$  contacts to the p-wells, in addition to the floating guard rings that terminate the edges. All implants are performed at 1600 °C in Ar. A 2 µm oxide layer is deposited and patterned to serve as the field oxide, which is followed by gate oxidation. A 500 Å thick gate oxide is thermally grown at 1200 °C in dry O<sub>2</sub>, then annealed in NO at 1175 °C for 2 hours, as described in [10]. Next, a 0.25 µm molybdenum layer is sputtered and patterned for the gate metal. The contacts to the source, drain, and p<sup>+</sup> regions are formed with alloyed Ni. The gate is then metallized with a 0.25 µm thick Ni/Au layer to reduce the gate resistance. A Plasma-Enhanced Chemical Vapor Deposition (PECVD) oxide layer is then deposited as an inter-metallic dielectric, and via holes are opened for the contacts. Finally, a 2 µm thick Ti/Pt/Au layer is deposited using e-beam evaporation and then liftedoff as the final metal layer.

**MOSFET Channel Currents On-State Equations**  $V_{dds} = V_{ds} + I_d \left( R_b + R_s \right)$  $I_{mos} = I_{mosh} + I_{mosl}$  $R_b = \frac{W}{qAN, \mu}$  where  $W = W_b - W_{dsj}$  $V_{Th} = V_T + \frac{K_{fl}}{1 - K_a} dV_{TT}$  $\mu_{n}(T) = \frac{947}{1 + \left(\frac{N_{b}}{1.94 \cdot 10^{17}}\right)^{0.61}} \cdot \left(\frac{T}{300K}\right)^{-2.15}$  $V_{\tau\tau} = V_{\tau} - dV_{\tau\tau}$ **Transient Equations** Linear Region:  $W_{dsj} = \sqrt{\frac{2\varepsilon_{semi}(V_{ds} + V_{bi})}{aN_{s}}}$  $y = \frac{K_f}{K_f - \frac{P_{vf}}{K_f}}$  $C_{dsj} = A_{ds} \varepsilon_{semi} / W_{dsj}$  where  $A_{ds} = A - A_{gd}$ for  $V_{ds} \leq \frac{V_{gs} - V_{ll}}{P_{ds}} \mid C_{gdj} = A_{gd} \varepsilon_{semi} / W_{gdj}$  $I_{mosh} = \frac{(1 - K_{fl})K_{f}K_{p} \left[ (V_{gs} - V_{Th})V_{ds} - P_{ef}^{y-1}V_{ds}^{y}(V_{gs} - V_{Th})^{2-y} \right]}{(1 + \theta(V_{gs} - V_{Th}))} \quad | \quad C_{gd} = \begin{cases} C_{oxd} \\ C_{oxd}C_{gdj} / (C_{oxd} + C_{gdj}) \\ V_{ds} > V_{gs} - V_{Td} \end{cases}$  $\begin{array}{c|c} \text{for} \quad V_{ds} \leq \frac{V_{gs} - V_{ih}}{P_{vf}} \quad \\ \end{array} \begin{vmatrix} C_{gi} = \begin{cases} C_{oxd} \\ C_{oxd} \begin{pmatrix} V_{gs} - V_{Tdiedge} \\ V_{--} - V_{--} \end{pmatrix} & \text{for} \quad V_{gs} \leq V_{Tdiedge} \\ V_{gs} < V_{Tdiedge} & V_{Tdiedge} > V_{Tdi} \end{cases}$ Saturation Region:  $I_{mosl} = \frac{K_{fl}K_{\rho}(V_{gs} - V_{fl})^{2}}{2(1 + \theta(V_{gs} - V_{fl}))} \qquad \text{for } V_{ds} > \frac{V_{gs} - V_{il}}{P_{os}} \qquad \left| \begin{array}{c} V_{Tdi} = V_{Td} - V_{bigd} - \frac{F_{sjbm}A_{gd}}{C_{osd}} \sqrt{2\varepsilon_{semi}qN_{b}(V_{bigd} + V_{ds})} \right|$  $I_{mash} = \frac{(1 - K_{fl})K_{p}(V_{gs} - V_{Th})^{2}}{2(1 + \theta(V_{gs} - V_{Th}))} \quad \text{for } V_{ds} > \frac{V_{gs} - V_{th}}{P_{r,s}}$   $V_{Tdiedge} = V_{Td} - V_{bigd} - \frac{F_{sjbe}A_{gd}}{C_{oxd}}\sqrt{2\varepsilon_{semi}qN_{b}(V_{bigd} + V_{ds})}$

#### **III. POWER MOSFET MODEL DESCRIPTION**

The model used in this work is based upon the latest version of the power MOSFET formulation utilized in the Hefner IGBT model [5]. The model has been enhanced by adding the temperature dependent material properties of 3C-, 4H-, and 6H-SiC, which can be selected using the material type parameter switch. The model contains features that have been shown to be important to describe the dynamic performance of vertical power MOSFETs including the twophase nonlinear gate-drain overlap capacitance, negative gate voltage inversion of the gate-drain overlap, and nonlinear body-drain depletion capacitance. The MOSFET channel current expressions used in the model are unique in that they include: (1) the channel regions at the corners of the square or hexagonal cells that turn on at lower gate voltages and (2) the enhanced linear region transconductance due to diffusion in the nonuniformly doped channel. The enhanced linear region transconductance is particularly important for the SiC power MOSFET as described in the results section below.

# A. On-State Model Characteristics

Table I gives the basic equations used in the model. The left-hand side of Table I gives the MOSFET channel currentrelated equations, and the right-hand side gives the on-state voltage and transient-related equations. The MOSFET channels in parallel; one that dominates in the very low current region,  $I_{mosl}$ , due to conduction at the corners of the MOSFET cells and another that dominates in the high current region,  $I_{mosh}$ , due to the main portion of the MOSFET cells. The corner regions have a lower threshold voltage and transconductance than the main channel resulting in a "soft threshold" effect. Therefore, it is necessary to assign each region a unique threshold voltage,  $V_{Tl}$  and  $V_{Th}$ , and transconductance factor  $K_{fl}$  and  $(1 - K_{fl})$ , through the use of the additional parameters  $K_{fl}$  and  $dV_{Tl}$ . The expressions for  $V_{Tl}$  and  $V_{Th}$  are formulated to simplify parameter extraction and to allow the model to reduce to the same parameter set in the high current region with or without the soft threshold effect.

The linear region expressions for  $I_{mosl}$  and  $I_{mosh}$  include the effect of carrier diffusion in the channel due to nonuniform channel dopant density. This effect yields different values for the linear region and saturation region transconductance parameters. The model incorporates this effect using a saturation region transconductance parameter  $K_p$  and a linear region transconductance factor  $K_f$ , where  $K_f$  is the ratio of the linear region transconductance parameter to the saturation region transconductance parameter. The transition between the saturation and linear region or "pinchoff region" is further refined by the pinch-off voltage parameter  $P_{yf}$ . The expressions for  $I_{mos}$  and y in the linear region are formulated such that the current and its first derivative are continuous at the pinch-off voltage. Both the linear and saturation region expressions include the reduction in channel mobility due to the high transverse electric field for high gate voltages through the parameter  $\theta$ .

The drain-source terminal voltage  $V_{dds}$  consists primarily of the voltage across the MOSFET channel  $V_{ds}$ , the voltage across the epitaxial layer resistance  $R_b$ , and the voltage across the source series contact resistance  $R_s$ . The main advantage of the SiC MOSFET compared to the Si MOSFET is that the value of  $R_b$  is reduced because a larger value of  $N_b$  and a smaller value of  $W_b$  can be used for a given device blocking voltage rating. The temperature dependence of SiC bulk mobility  $\mu_n(T)$  has been studied extensively by others [11] and is important in determining the on-state voltage. The bulk

| Filthysical Constants                          | EER                   |

|------------------------------------------------|-----------------------|

|                                                | ALCULATE)             |

| ## \$1,450E+10                                 | em 9                  |

| <i>wp</i> €1500                                | cm <sup>2</sup> 2/V s |

| e si \$1.050E-12                               | F/cm                  |

| <i>a J</i> ∰1.429€+20<br><i>a Z</i> ∰4.540€+11 | (cm ¥ s)~1<br>cm \$1  |

| P. MAN \$1.100E+7                              | em/s                  |

| P. OKAY \$9.500E+6                             | fon/s                 |

|                                                |                       |

|                                                | SI SI                 |

|                                                | 4H SIC                |

| <u>1.</u>                                      | 6HSiC                 |

Fig. 2. Temperature dependent material parameters for 4H-, 6H-, and 3C-SiC added to IMPACT extraction tools.

mobility varies with the SiC polytype and is given in Table I for 4-H SiC. This is one of the material properties that is selected using the material type parameter switch in the model.

# **B.** Transient Model Characteristics

The transient characteristics of the model are described by the depletion and oxide capacitance equations in Table I, in addition to the constant gate-source capacitance  $C_{gs}$  due to the gate-source overlap and gate metallization capacitance. The drain-source junction capacitance  $C_{dsj}$  is determined by the drain-body depletion width  $W_{dsj}$  and the area of the drainbody junction  $A_{ds}$ . The depletion capacitance depends on the value of the drift region dopant density  $N_b$  and the built-in potential of the junction  $V_{bi}$ . The built-in potential is a function of the temperature dependent intrinsic carrier concentration  $n_i$  for the material.

The gate-drain capacitance  $C_{gd}$  has a depletion capacitance component that depends on the gate-drain overlap area  $A_{gd}$  and the gate-drain overlap depletion threshold  $V_{Td}$ . For drain-gate voltages  $(V_{ds} - V_{gs})$  less than - $V_{Td}$ ,  $C_{gd}$  is equal to the gate-drain overlap oxide capacitance  $C_{oxd}$ . For drain-gate voltages greater than  $-V_{Td}$ ,  $C_{gd}$  is equal to the series combination of  $C_{gdj}$  and  $C_{oxd}$ . For sufficiently negative gate voltages, an inversion layer forms beneath the gate-drain overlap, resulting in a capacitance from the gate to the inversion layer,  $C_{gi}$ . Because the gate-drain overlap inversion layer contacts the body region that is shorted to the source contact, the main effect of the inversion capacitance is to increase the gate-source capacitance. For  $V_{gs} < V_{Tdiedge}$ , an inversion layer begins to form adjacent to the body-drain junction. The inversion layer capacitance increases linearly with increasing negative gate voltage until  $V_{gs} < V_{Tdi}$ , where the entire area beneath the gate-drain overlap becomes inverted and  $C_{gi}$  becomes equal to  $C_{oxd}$ . Both  $V_{Tdiedge}$  and  $V_{Tdi}$ are functions of the neck region built-in potential  $V_{bigd}$  that is calculated from the extracted value of the base doping  $N_b$ , the gate-drain overlap accumulation threshold voltage  $V_{Td}$ , and the fractions of gate-drain depletion charge imaged on the gate from the adjacent body regions both in the center of the neck region  $F_{xjbm}$  and at the body edge of the neck region F<sub>xjbe</sub>.

### **IV. PARAMETER EXTRACTION USING IMPACT**

Recently, a software package called IGBT Model Parameter ExtrACtion Tools (IMPACT) was introduced to automate laboratory instrument control and parameter determination for IGBTs [6]. To extend IMPACT to be applicable to SiC power MOSFETs, a material type switch was added to select and calculate the temperature dependent properties of the material as shown Fig. 2. For power MOSFETs, the IMPACT package reduces to three programs that extract the power MOSFET model parameters, as shown in Table II. These programs are SATMSR, which measures the saturation current versus gate voltage to extract  $K_{psat} \equiv K_{p}$ ,  $V_T$ ,  $\theta$ ,  $K_{fl}$ , and  $dV_{Tl}$ ; LINMSR, which measures the linear

| Parameter symbol                      | Parameter name                                       | Program | Extraction Characteristic        |

|---------------------------------------|------------------------------------------------------|---------|----------------------------------|

| A                                     | Device active area                                   |         | Chip Size                        |

| V <sub>T</sub>                        | Threshold voltage                                    | SATMSR  | Saturation current vs. Vgs       |

| $K_p = K_{psat}$                      | Saturation region transconductance                   |         | Saturation current vs. Vgs       |

| θ                                     | Transverse electric field parameter                  |         | High saturation current vs. Vgs  |

| $K_{fl}$                              | Low current transconductance factor                  |         | Low saturation current vs. Vgs   |

| $dV_{Tl}$                             | Low current threshold voltage differential           |         | Low saturation current vs. Vgs   |

| $K_{plin} = \overline{K_p \cdot K_f}$ | Linear region transconductance parameter             | LINMSR  | On-state voltage vs. Vgs         |

| $R_s$                                 | Drain series resistance                              |         | On-state voltage vs. Vgs         |

| N <sub>b</sub>                        | Drift region dopant density                          |         | On-state voltage vs. Vgs         |

|                                       | Gate-source capacitance                              | CAPMSR  | Gate charge at low gate voltage  |

| C <sub>gs</sub><br>C <sub>oxd</sub>   | Gate-drain overlap oxide capacitance                 |         | Gate charge at high gate voltage |

| A <sub>gd</sub>                       | Gate-drain overlap area                              |         | Gate-drain charge                |

| V <sub>Td</sub>                       | Gate-drain overlap depletion threshold               |         | Gate-drain charge                |

| $F_{xjbe}$                            | Gate-drain overlap depletion charge factor at edge   |         | Gate charge vs. Vgs              |

| F <sub>xibm</sub>                     | Gate-drain overlap depletion charge factor at middle |         | Gate charge vs. Vgs              |

TABLE II. IMPACT PROGRAMS AND EXTRACTION CHARACTERISTICS FOR MOSFET MODEL PARAMETERS

region on-state voltage versus gate voltage for a constant drain current to extract  $K_{plin} \equiv K_p K_f$ ,  $R_s$ , and  $N_b$ ; and CAPMSR, which measures gate and gate-drain charge characteristics to extract  $C_{gs}$ ,  $C_{oxd}$ ,  $A_{gd}$ ,  $V_{Td}$ ,  $F_{xjbm}$ , and  $F_{xjbe}$ . The values of  $W_b$  and A are assumed to be known from the device structure. The extraction sequence is performed over an applicable temperature range to extract the temperature coefficients of the model parameters.

# A. Saturation Region Parameter Extraction Using SATMSR

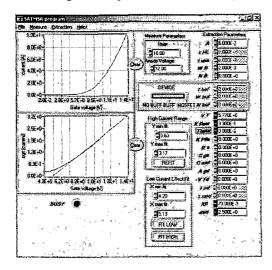

Fig. 3 shows the SATMSR front panel. In SATMSR, the saturation current versus gate voltage is used to extract the MOSFET transconductance parameters for the saturation region  $K_{psal}$ , the high current region  $\theta$ , the low current region  $K_{fl}$  and  $dV_{tl}$ , and the threshold voltage  $V_T$ . To perform the extraction, the MOSFET saturation current  $I_{mas}^{sat}$  is measured as a function of gate voltage, and the resulting square root of

Fig. 3. SATMSR front panel demonstrating extraction of  $K_p$ ,  $V_T$ ,  $\theta$ ,  $K_{fb}$ , and  $dV_{Tb}$ .

$I_{mos}^{sat}$  versus gate voltage is used to extract the model parameters. Commercial programmable semiconductor curve tracers are used to aid in the parameter extraction process. Since these instruments use the collector voltage as the sweep variable and the gate voltage as the step variable, the program uses the gate offset voltage and the cursor readout to generate the continuous graph of current versus gate voltage.

The front panel of the SATMSR program incorporates several pull-down menus that allow the user to perform different measurement functions according to the device characteristics and the curve tracer required for the current range of interest. The panel also allows the user to specify the maximum allowable device current  $I_{max}$  during the measurement and the anode voltage of interest  $V_{anode}$ . When a measurement is performed using the measure pull-down window, the gate voltage is varied, and the gate voltage and drain current values are transmitted to the computer for analysis.

After a measurement is performed, the user selects the extraction process from the extraction pull-down menu. The first extraction step performs a least squares fit to the simplified model equation

$$\sqrt{I_{mos}^{sat}} = \sqrt{\frac{K_{psat}}{2}} \left( V_{gs} - V_T \right). \tag{1}$$

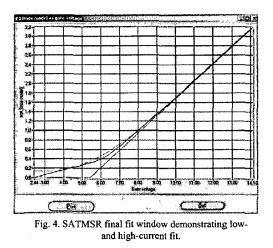

The resulting  $K_{psat}$  and  $V_T$  are displayed on the user interface parameter value list. The user can then extract the highcurrent parameter  $\theta$  and refine the extracted value of  $K_{psat}$ using the "Refine  $K_{psat}$  and  $\theta$ " button in the extraction pulldown menu. Next, the "Fit Low" and "Fit High" buttons are used to extract  $K_{fl}$  and  $dV_{tl}$ . These buttons perform a leastsquares fit to the saturation region's low- and high- current equations shown in the left-hand column of Table I. The lowand high-current ranges for the fits are estimated by the program but can be adjusted by the user. Fig. 4 demonstrates

the final fit of the square-root of the MOSFET saturation current to the saturation region measured data demonstrating the different slope in the high- and low-current regions.

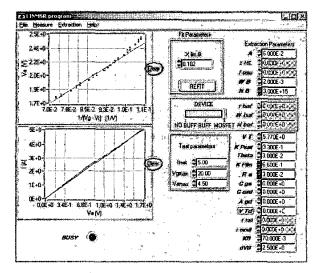

#### B. Linear Region Parameter Extraction Using LINMSR

Fig. 5 demonstrates the front panel of the LINMSR extraction program. In this program, the linear region on-state voltage versus gate voltage for a constant anode current is used to extract the linear region transconductance  $K_{plin}$ , the series resistance  $R_s$ , and the base dopant density  $N_b$ . These values are calculated from the model equations that are valid for the linear region where the values of the parameters extracted from the previous extraction steps (those from the SATMSR program) are used as known values in the equations.

Fig. 5. LINMSR front panel demonstrating extraction of  $K_{\beta}$   $R_s$ , and  $N_b$ .

Fig. 6. CAPMSR front panel demonstrating the extraction of  $C_{gs}$ ,  $C_{oxd}$ ,  $A_{gds}$ and  $V_{Td}$ .

To perform the measurement, the user enters the test current  $I_T$ , the maximum gate voltage  $V_{gmax}$ , and the maximum anode voltage  $V_{amax}$  on the user interface. Since the programmable semiconductor curve tracers apply voltage and measure current, LINMSR uses an iteration algorithm to establish the constant drain test current, which is described in [6]. The iteration results in measuring the on-state drain voltage that results in the selected current for each gate voltage.

After the measurement is performed, the extraction is performed using a least-squares fit to the extraction equation that is valid in the linear region of operation:

$$V_{on} = V_r + \frac{I_T}{K_{plin} \left( V_{gs} - V_T \right)} \tag{2}$$

where

$$V_r = (R_b + R_s)I_d + \frac{I_d\theta}{K_{plin}}.$$

(3)

The slope of the linear fit determines  $K_{plin}$  and the intercept determines  $V_r$ . Using the extracted value of  $V_r$  and the parameters extracted from the previous steps, the value of  $N_b$  is calculated using the expression for  $R_b$  in Table 1. These extracted values are displayed in the list of parameters on the user interface.

### C. Gate Charge Characteristics Extraction Using CAPMSR

Fig. 6 demonstrates the front panel for the CAPMSR program. This program uses the gate- and gate-drain charge characteristics to extract the gate-source capacitance  $C_{gs}$ , the gate-drain overlap oxide capacitance  $C_{oxd}$ , the gate-drain overlap area  $A_{gd}$ , and the gate-drain overlap depletion threshold  $V_{Td}$  as described in [12]. The program uses the extraction equation

$$C(V) = \frac{I}{\frac{dV}{dt}} \tag{4}$$

to extract the above listed parameters. The user controls the minimum value of dV/dt and the number of derivative points for each calculation. The values of  $C_{gs}$  and  $C_{oxd}$  are determined from  $I_g$  and  $dV_{gs}/dt$  during the first and second phase of the gate charge curve respectively. The values of  $V_{Td}$  and  $A_{gd}$  are determined by  $I_g$  and  $dV_{dg}/dt$  during the plateau portion of the gate charge curve. Finally, the values of  $F_{xjbm}$  and  $F_{xjbm}$  are determined by  $I_g$  and  $dV_{gs}/dt$  for negative gate voltages and different drain voltages.

# V. MEASURED AND SIMULATED RESULTS

In this section, the model presented in Section III is used to describe the performance of a 2 kV, 5 A 4H-SiC Double implanted MOSFET (DiMOSFET) as described in Section II and to perform a detailed comparison with the performance of a widely used 400 V, 5 A Si Vertical Double-Diffused MOSFET (VDMOSFET). To do this, the model parameters are extracted for each device at several temperatures using the extraction sequence described in Section IV. Table III shows the parameters extracted for the Si and SiC MOSFETs at 25 °C.

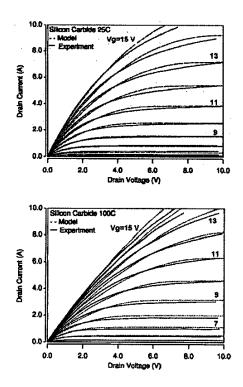

Fig. 7. Silicon carbide MOSFET simulated (dashed) and measured (solid) output characteristics as a function of gate voltage for (a) 25 °C and (b) 100 °C.

# TABLE III. MODEL PARAMETERS AT 25 °C

| Parameter         | Si                           | SiC                                 |

|-------------------|------------------------------|-------------------------------------|

| A                 | $0.1 \ cm^2$                 | 0.06 cm <sup>2</sup>                |

| Wb                | 50 µm                        | 20 µm                               |

| Nb                | $3.1 \cdot 10^{14}  cm^{-3}$ | 3 10 <sup>15</sup> cm <sup>-3</sup> |

| VT                | 3.4 V                        | 5.77 V                              |

| K <sub>p</sub>    | $3.3 A/V^2$                  | $0.33 \ A/V^2$                      |

| θ                 | 0                            | 0.03 V'                             |

| K <sub>f</sub>    | 1.7                          | 2                                   |

| R <sub>s</sub>    | $0.02 \ \Omega$              | 0.03 <i>Q</i>                       |

| KſI               | 0                            | 0.07                                |

| $dV_{ii}$         | 0 V                          | 2.5 V                               |

| Pvf               | 0.7                          | 0.95                                |

| V <sub>Td</sub>   | 3.4 V                        | 0 V                                 |

| Agd               | $0.075 \ cm^2$               | $0.03 \ cm^2$                       |

| $C_{gs}$          | 1.114 nF                     | 2.68 nF                             |

| Caxd              | 2.066 nF                     | 2.18 nF                             |

| Voted             | 0.6 V                        | 2.8 V                               |

| Fxjbe             | 0.5                          | 0.5                                 |

| F <sub>xjbm</sub> | 0.75                         | 0.75                                |

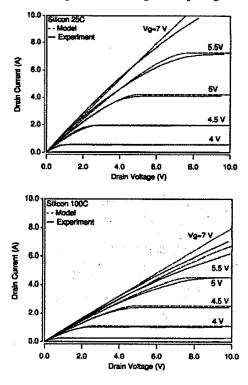

## A. Steady-State Output Characteristics

Figs. 7 and 8 show the simulated and measured output characteristics for the 2 kV SiC and 400 V Si MOSFETs at 25 °C and 100 °C. The on-state resistance at 25 °C is similar between the Si and SiC MOSFETs, although the SiC device requires twice the gate drive voltage. Comparing the SiC and

Fig. 8. Silicon MOSFET simulated (dashed) and measured (solid) output characteristics as a function of gate voltage for (a) 25 °C and (b) 100 °C.

Si on-state curves, the Si curves are linear in the on-state region and have a pronounced change in curvature as the saturation or pinch-off region is approached. This occurs because the Si power MOSFET has a large epitaxial layer resistance in series with the MOSFET channel and the channel has a very high transconductance. This causes the Si device to exhibit a resistive-type slope in the linear region prior to pinch-off.

The SiC curves on the other hand, gradually transition from the linear region to the saturation region. In SiC MOSFETs, the epitaxial layer resistance is much smaller and the channel resistance is higher, thus making the MOSFET channel a more significant contributor to the on-state voltage. This is due to the low channel surface mobility of SiC compared to Si. Because the SiC curves have less resistance in series with the MOSFET channel, the enhanced linear region transconductance model of [5] is essential for these devices. Furthermore, because the transconductance is much smaller for SiC, the on-state voltage is closer to the pinch-off voltage, and the model for the transition region is more important.

At 100 °C, the Si device has a severe reduction in conduction capability, whereas the SiC on-resistance is only minimally affected. This occurs because the drift region resistance is a smaller portion of the on-state resistance in the SiC device and because the channel mobility does not decrease with temperature for the SiC device. In the SiC MOSFET, the channel mobility increases with temperature as more interface traps become occupied with the larger concentration of electrons available for conduction, whereas the bulk mobility decreases with temperature as carrier scattering dominates [9]. The resulting effect is an increase in channel conductance  $K_p$  and  $K_{f5}$  and an increase in the drift layer series resistance  $R_b$ .

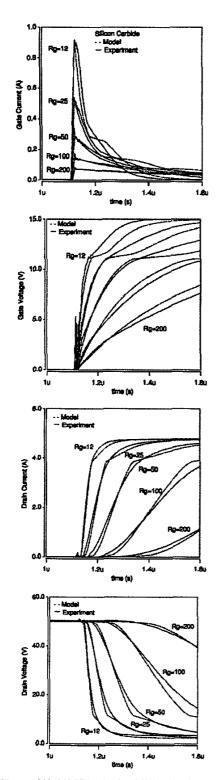

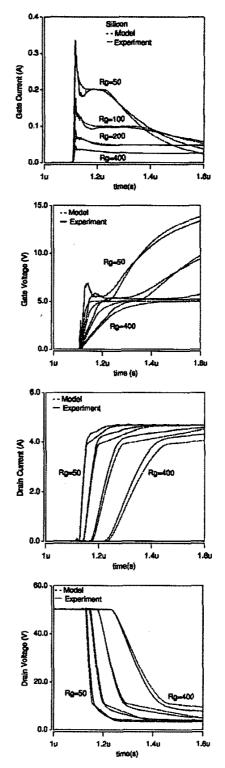

# B. Transient Switching Waveforms

Figs. 9 and 10 show the Si and SiC MOSFET simulated and measured turn-on waveforms versus gate resistance under resistive load conditions [13]. The simulated test circuit emulates the well-characterized test circuit using a gate driver with a 15 ns rise time to 15 V, a gate inductor  $L_g = 10$  nH, a drain series resistor  $R_L \approx 10 \Omega$ , a drain series inductor  $L_L = 1$ nH, and a drain supply voltage of 50 V. The gate resistor  $R_g$ was varied to provide different turn-on speeds for the devices.

The turn-on process begins with the driver circuit ramping to 15 V. Gate current immediately begins to flow as the gate capacitances  $C_{gs}$  and  $C_{gd}$  are charged. Once  $V_{gs}$ increases to the threshold voltage  $V_T$ , current begins to increase through the drain and the drain voltage begins to fall. As the drain voltage drops, the gate voltage remains relatively constant (plateau region) as the gate current charges the gatedrain capacitance. The charging of the gate-drain capacitance occurs in two phases: in the first phase for high drain voltages, the drain voltage falls more rapidly because  $C_{gd}$  is dominated by the depletion capacitance and is relatively small, then in the second phase when  $V_{gd}$  becomes less than  $V_{Td}$ , the drain voltage falls more slowly because  $C_{gd}$  is equal to  $C_{oxd}$  and is much larger. As the drain voltage begins to approach the on-state voltage,  $C_{gd}$  is not being charged and the gate voltage begins to rise again toward the gate supply voltage as  $C_{gs}$  and  $C_{oxd}$  are charged.

The turn-on waveforms are similar for the Si and SiC MOSFETs except that the SiC MOSFET requires one-half the gate resistance to achieve the same speed because the gate capacitance parameters are approximately twice as large. The same speed could also be achieved using the same gate resistors but with twice the gate drive voltage for the SiC MOSFET as compared to the Si MOSFET. The ion implantation method used to construct the DiMOSFET results in shallower p-well depths with less resistance between the p-wells. As a result, the gate-drain overlap area  $A_{gd}$  in the SiC DiMOSFET can be made much smaller than for the Si VDMOSFET. Furthermore, neck region implants can be avoided, resulting in a reduction in  $V_{Td}$ . This results in a lower effective  $C_{gdb}$  which increases the speed during the plateau region.

# **VI.** CONCLUSION

A power MOSFET model applicable to Si and SiC power MOSFETs was presented. Results were shown for a widely used 400 V, 5 A Si power VDMOSFET and a new 2 kV, 5 A SiC power DiMOSFET. The model was validated for the forward conduction and switching characteristics over a wide temperature range. The results demonstrate good agreement between the model and experiment for both technologies. The IMPACT parameter extraction tools were extended to be applicable to the power MOSFET model parameter extraction sequence and the SiC material parameters.

The SiC MOSFET demonstrated similar on-state performance to that of the Si VDMOSFET while having a five times larger blocking voltage and a better ability to maintain forward conduction capability at high temperatures. The switching performance was similar for the Si and SiC devices except that the SiC device required twice the gate drive voltage. The new model provides insights into the SiC MOSFET performance and provides the capability to simulate the performance of the new technology in different circuit applications.

# ACKNOWLEDGEMENTS

The work was supported in part by the DARPA Wide Bandgap Power Device Semiconductor Program, managed by Dr. John Zolper; the National Science Foundation Grant # ECS-0115534, managed by Dr. Usha Varshney; and the DARPA/ONR contract #N00014-99-C-0377, managed by Dr. Daniel Radack and monitored by Dr. George Campisi. The authors also wish to acknowledge Professor Kraig Olejniczak for his efforts in helping to develop the Semiconductor Device Modeling Group at the University of Arkansas.

Fig. 9. Silicon carbide MOSFET simulated (dashed) and measured (solid) turn-on waveforms as a function of gate resistance: (a) gate current, (b) gate voltage, (c) drain current, and (d) drain voltage.

Fig. 10. Silicon MOSFET simulated (dashed) and measured (solid) turn-on waveforms as a function of gate resistance: (a) gate current, (b) gate voltage, (c) drain current, and (d) drain voltage.

#### REFERENCES

- A.R. Hefner, R. Singh, J.S. Lai, D.W. Berning, S. Bouche, C. Chapuy, "SiC Power Diodes Provide Breakthrough Performance for a Wide Range of Applications," *IEEE Trans. on Power Electronics*, vol. 16 no. 2, pp. 273 – 280, March 2001.

- [2] T. McNutt, A. Hefner, A. Mantooth, J. Duliere, D. Berning, R. Singh, "Silicon-Carbide PiN, Schottky, and Merged PiN-Schottky Power Diode Models Implemented in the Saber Circuit Simulator," Conf. Rec. of IEEE Power Electronics Specialists Conf (PESC), pp. 2103-2108, Vancouver, Canada, June 2001.

- [3] Saber is a registered trademark of Synopsys Inc., 2025 NW Cornelius Pass Rd., Hillsboro, OR 97124. Certain commercial products or materials have been identified in order to specify or describe the subject matter of this paper adequately. This does not imply recommendation or endorsement by the National Institute of Standards and Technology, nor does it imply that these products are the best for the purpose.

- [4] T. McNutt, A. Hefner, A. Mantooth, J. Duliere, D. Berning, R. Singh, "Parameter Extraction Sequence for SiC Schottky, Merged PiN Schottky, and PiN Power Diode Models," *Conf. Rec. of IEEE Power Electronics Specialists Conf (PESC)*, pp. 1269-1276, Cairns, Australia, June 2002.

- [5] A.R. Hefner, "Modeling Buffer Layer IGBT's for Circuit Simulation," *IEEE Transactions on Power Electronics*, vol. 10, no. 2, pp. 111-123, March 1995.

- [6] A.R. Hefner, S. Bouché, "Automated Parameter Extraction Software for Advanced IGBT Modeling," Proceedings of The 7<sup>th</sup> Workshop on Computers in Power Electronics (COMPEL), Blacksburg, VA, July 2000.

- [7] P.G. Neudeck, "Progress in Silicon Carbide Semiconductor Electronics Technology," J. Electron. Mater., vol. 24, p. 283, 1995.

- [8] M. Bhatnagar, B.J. Baliga, "Comparison of 6H-SiC, 3C-SiC, and Si for Power Devices," *IEEE Trans. ED*, vol. 40, no. 3, p. 645, March 1993.

- [9] S.H. Ryu, A. Agarwal, J. Richmond, J. Palmour, N. Saks, J. Williams, "27 mΩ-cm<sup>2</sup>, 1.6 kV Power DiMOSFETs in 4H-SiC," Proceedings of the International Symposium on Power Semiconductor Devices (ISPSD), Santa Fc, NM, June 2002.

- [10] G. Chung, C.C. Tin, J.R. Williams, J.K. McDonald, M. Di Ventra, S.T. Pantelides, L.C. Feldman, R.A. Weller, "Effect of Nitric Oxide Annealing on the Interface Trap Densities Near the Band Edges in the 4H Polytype of Silicon Carbide," *Applied Physics Letters*, 76(13) pp. 1713-1715, March 2000.

- [11] W. Choyke, H. Matsunami, G. Pensl, (eds.) SiC: A Review of Fundamental Questions and Applications to Current Device Technology, Akademie Verlag, Vol. II, 1997.

- [12] A.R. Hefner, "Semiconductor Measurement Technology: INSTANT - IGBT Network Simulation and Transient Analysis Tool," NIST Special Publication 400-88, 1992.

- [13] I. Budihardjo, P.O. Lauritzen, and H.A. Mantooth, "Performance Requirements for Power MOSFET Models," *IEEE Trans. on Power Electronics*, pp. 36-45, vol. 12, no. 1, Jan. 1997.