# The Role of Carrier Lifetime in Forward Bias Degradation of 4H-SiC PiN Diodes

Allen Hefner<sup>1</sup>, Ty McNutt<sup>2</sup>, Dave Berning<sup>1</sup>, Ranbir Singh<sup>1</sup> and Adwoa Akuffo<sup>3</sup>

<sup>1</sup> National Institute of Standards and Technology<sup>†</sup>, 100 Bureau Dr., Gaithersburg, MD, 20899

<sup>2</sup> University of Arkansas, Dept. of Electrical Engineering, Fayetteville, AR, 72701

<sup>3</sup> Howard University, Dept. of Electrical Engineering, NW, Washington, DC 20059

**Keywords:** SiC, PiN diode, forward bias degradation, lifetime, stacking fault, high voltage, power device, reverse recovery, transient waveform, end-region recombination, parameter extraction.

Abstract. The role of excess carrier lifetime reduction in the mechanism for on-state voltage  $(V_f)$  degradation of high voltage 4H-SiC PiN diodes is investigated. A method is developed to electrically monitor the emitter, base, and end region excess carrier lifetimes at periodic intervals during the forward bias stress condition. The lifetime measurement method involves using the turn-off reverse-recovery waveforms for conditions of high dI/dt and low dV/dt. The peak reverse-recovery current for high dI/dt is related to the excess carrier charge stored before the diode is switched off and is an indication of the total recombination rate. The low dV/dt condition minimizes the carrier sweep out and diffusion currents resulting in a current tail with a decay rate that is determined by the base and end-region lifetimes. This lifetime measurement method is used to monitor diodes with degradation times ranging from one minute to over several hundred hours. The measurements indicate that  $V_f$  degradation is accompanied by a reduction in end region lifetime and/or reduction in device conduction area.

## Introduction

Recently, Silicon-Carbide (SiC) power diodes have begun to emerge with breakthrough static and dynamic performance compared to existing Silicon (Si) power diodes [1-3]. For medium voltage applications (< 3 kV), majority carrier devices such as Schottky diodes and MOSFETs have the best performance, whereas conductivity modulated bipolar type devices generally provide better performance for higher voltage applications. Although rapid progress has been made towards commercialization of majority carrier SiC Schottky power diodes, a potential challenge to the commercialization of high-voltage conductivity modulated SiC power devices is the degradation of the on-state voltage ( $V_f$ ) with forward bias stress. It is generally recognized that propagation of SiC crystal stacking faults is the origin of  $V_f$  degradation [4] although the mechanism by which the electrical properties of the material and device are changed has not been well established. The purpose of this paper is to facilitate the study of the  $V_f$  degradation mechanism by providing a method of electrically monitoring the excess carrier lifetimes in various regions of the device at periodic intervals during the forward bias stress.

## Forward Bias Degradation Mechanism

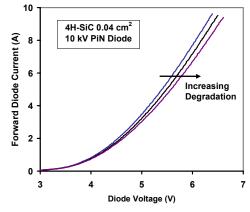

Figure 1 shows the on-state characteristics of a high voltage SiC PiN diode after various levels of forward bias stress. The magnitude of increase in  $V_f$  is dependent on the length of time and the amount of forward current flowing through the diode [5]. The  $V_f$  degradation time for the devices studied in this work ranged from few milliseconds to many hours [6]. Our measurements indicate that the amount of degradation is generally not influenced by switching or by reverse bias blocking

<sup>&</sup>lt;sup>†</sup> Contribution of the National Institute of Standards and Technology; not subject to copyright.

and is only a function of the total amount of time a device is operated at a given current. The amount of degradation is generally observed to be proportional to the current-time product and increases with increased temperature during stress, although the degradation rate can also exhibit some sporadic behavior due to initiation and termination of individual stacking fault propagations.

Optical observation of PiN diodes undergoing  $V_f$  degradation have demonstrated the simultaneous formation of mobile and propagating crystal stacking faults [4,6,7,8]. It is now established that these mobile stacking faults nucleate from existing substrate crystal

Fig. 1. PiN diode forward bias degradation.

defects and process induced defects in hexagonal (eg. 4H and 6H) SiC. It has also been established that the energy from electron-hole pair recombination provides the activation energy necessary for the propagation of the stacking faults. This is substantiated by the activation energy of 0.27 eV calculated from emission spectrum measurements [4]. It is also generally believed that the edges of the stacking faults act as recombination centers that reduce the carrier lifetime in the material and lead to the observed on-state voltage degradation [7]. It is the purpose of this paper to further investigate the lifetime reduction hypothesis by monitoring the lifetime in various regions of the device during the degradation.

### **Lifetime Measurement Method**

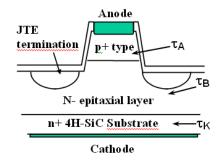

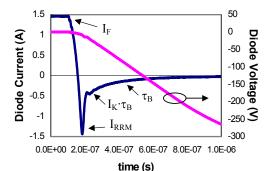

In this section, a method of electrically monitoring the emitter, base, and end-region lifetimes ( $\tau_A$ ,  $\tau_B$ , and  $\tau_K$ , respectively) is introduced. Figure 2 is a diagram of a PiN diode indicating the location of each lifetime region. The lifetime measurement method involves using the turn-off reverse-recovery waveforms for conditions of high *dI/dt* and low *dV/dt* where the high *dI/dt* is obtained using a vacuum tube driver and *dV/dt* is controlled using a capacitor across the driver [3]. Figure 3 shows the reverse-recovery current and voltage waveforms indicating the features of the waveforms used to measure the lifetimes. The current waveform consists of an initial reverse-recovery peak followed by a slowly decaying tail. The peak reverse-recovery current *I<sub>RRM</sub>* for high *dI/dt* is related to the excess carrier charge and is an indication of the total recombination rate from the emitter, base, and end regions.

The low dV/dt condition obtained using the added driver capacitance minimizes the carrier sweep out current due to the moving depletion edge boundary and the low voltage condition results in a wide neutral base region minimizing the diffusion currents through the base toward the emitter and end regions. As a result, the current tail is larger and the tail decay rate ( $d\ln I/dt$ ) is determined by recombination in the base and end regions as expressed by the following equations [9,10]:

$$\frac{d\ln I}{dt} = \frac{1}{\tau_B} \left( 1 + \frac{I}{I_K} \right) \qquad (1) \qquad \qquad I_K \tau_B = qA \frac{D_{pB}}{\sqrt{D_{pK}}} \frac{n_i^2}{n_{iK}^2} N_K \sqrt{\tau_K} \qquad (2)$$

where *I* is the tail current,  $I_K$  is the knee current beyond which end-region recombination becomes dominant, *A* is the diode active area,  $D_{pB}$  and  $D_{pK}$  are the base and end-region hole diffusivities,  $n_i$ and  $n_{iK}$  are the base and end-region intrinsic carrier concentrations, and  $N_K$  is the end-region dopant density. The IMPACT model parameter extraction tools [11] are used to perform the measurements, calculate the decay rate derivative, and perform a least squares linear fit to extract  $\tau_B$  and  $\tau_B I_K$ .

Fig. 2. Diagram of PiN diode indicating the location of each lifetime region.

Fig. 3. Low dV/dt reverse-recovery waveforms indicating the features used to monitor lifetime.

#### **Results and Discussion**

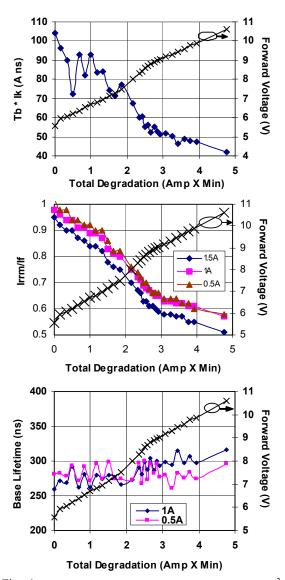

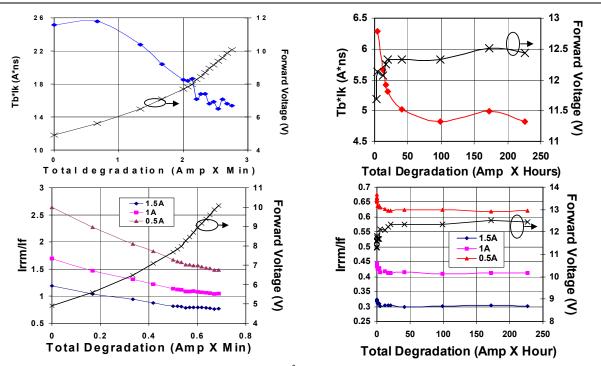

Diodes with degradation times ranging from one minute to over several hundred hours are studied. Figure 4 is an example of the measurement of  $V_f$ ,  $\tau_B$ ,  $\tau_B I_K$ , and  $I_{RRM}/I_F$  for a 10 kV, 0.01 cm<sup>2</sup> device stressed at 100 A/cm<sup>2</sup>. The extracted value of  $\tau_B$  is shown for two values of  $I_F$ , and  $I_{RRM}/I_F$  is shown for three values of  $I_F$ . The data indicates that  $\tau_B I_K$  and  $I_{RRM}/I_F$  decrease,  $V_f$  increases and  $\tau_B$  is relatively constant as the device is stressed.

The relatively constant  $\tau_B$  implies that the highlevel injection lifetime in the base is not reduced although the overall decay time is reduced (i.e.,  $\tau_B I_K$  and the second term in eq (2) dominate for the current range of interest). From Fig. 4a and eq (2), one can conclude that  $\tau_K$  and/or active conduction area A are decreased as the device is stressed (reduced A results in increased recombination because the charge per area is higher making end region recombination more important). The decrease in  $I_{RRM}/I_F$  of Fig. 4b indicates that the base charge is reduced due to the reduction of  $\tau_A$ ,  $\tau_K$ , and/or A. This decrease in base charge reduces the base region conductivity modulation and thus increases the  $V_f$  as indicated by the data.

Additional degradation results are given in Fig. 5 for a 0.04 cm<sup>2</sup> device from the same lot as the 0.01 cm<sup>2</sup> device of Fig. 4, and in Fig. 6 for a 0.01 cm<sup>2</sup> new low degradation rate device type [2]. Another 0.01 cm<sup>2</sup> low degradation rate device from the same lot as the device of Fig. 6 (not shown) had a  $V_f$  of 6.5V@100A/cm<sup>2</sup> and the  $V_f$ ,  $\tau_B I_K$ , and  $I_{RRM}$  / $I_F$  did not degrade after 300 Amp-Hours, whereas the device of Fig. 6 degraded and then stabilized.

Fig. 4. Degradation measurements for a 10kV, 0.01 cm<sup>2</sup> device stressed at 100 A/cm<sup>2</sup> indicating V<sub>f</sub> @ 1A on each graph and a)  $\tau_B I_K$  extracted at  $I_F = 1$  A, b)  $I_{RRM}$  / $I_F$  for three values of  $I_F$ , and c)  $\tau_B$  extracted at two values of  $I_F$ .

Fig. 5. Degradation measurements for a 10kV, 0.04 cm<sup>2</sup> device from the same lot as the device in Fig.3 stressed at 100 A/cm<sup>2</sup> indicating V<sub>f</sub> @ 1A on each graph and a)  $\tau_B I_K$  extracted at  $I_F = 1$  A, and b)  $I_{RRM} / I_F$  for three values of  $I_F$ .

Fig. 6. Degradation measurements for a 10kV, 0.01 cm<sup>2</sup> device stressed at 300 A/cm<sup>2</sup> indicating V<sub>f</sub> @ 1A on each graph and a)  $\tau_B I_K$  extracted at  $I_F$  = 1 A, and b)  $I_{RRM}$  /I<sub>F</sub> for three values of  $I_{F}$ .

The separation of the  $I_{RRM}/I_F$  curves in Figs. 5 and 6 indicate that these devices are dominated more by  $\tau_K$  and  $\tau_A$  than the device of Fig. 4.

#### Conclusions

A new lifetime measurement method is introduced and used to monitor diodes with degradation times ranging from one minute to over several hundred hours. Individual extraction of the emitter, base, and end-region lifetimes suggests that the effective end-region lifetime and/or conduction area are reduced. The reduction in lifetimes and/or conduction area results in a reduced charge to modulate the base conductivity resulting in the increased forward voltage drop.

*Acknowledgment:* The authors wish to thank Mrinal Das of Cree Inc. for providing the low degradation rate diodes and to acknowledge the DARPA Wide Bandgap Power Device Program managed by John Zolper for funding the work.

#### References

- [1] R. Singh, K. Irvine, C. Capell, J. Richmond, D. Berning, A. Hefner, J. Palmour, IEEE TED, vol. 49 (2002) p. 2308.

- [2] M. Das, et al., "High Power 4H-SiC PiN Diodes with Minimal Voltage Drift," ICSCRM, 2003.

- [3] A. Hefner, R.Singh, J.S. Lai, D.W. Berning, S. Bouche, and C. Chapuy IEEE, TPE, vol. 16, 2001, p. 273.

- [4] A. Galeckas, L. Linnros and P. Pirouz, Applied Physics Letters, vol. 81 (2002) p. 883.

- [5] A. Konstantinov, and H. Bleichner, Journal of Applied Physics, vol. 71 (1997) p. 3700.

- [6] R. Stahlbush, et al., Materials Science Forum, vols. 389-393, 2002. p. 427.

- [7] J. Bergman, H. Lendenmann, P. Nilsson, U. Lindefelt, P. Skytt, Mat. Science Forum, vols. 353-356, 2001. p. 299.

- [8] M. Skowrownski, et al., Journal of Applied Physics, vol 92, 2002. p. 4699.

- [9] A. Hefner, D Blackburn, Solid-State Electronics, vol. 31 (1988) p. 1513.

- [10] A. Hefner, IEEE Trans. Industry Appl. vol. 30 (1994) p. 394.

- [11] A. Hefner, S. Bouché, Workshop on Computers in Power Electronics (COMPEL), July 2000.