# 1 V and 10 V SNS Programmable Voltage Standards for 70 GHz

F. Mueller, R. Behr, T. Weimann, L. Palafox, *Senior Member, IEEE*, D. Olaya, P. D. Dresselhaus, and S. P. Benz, *Senior Member, IEEE*

Abstract—Programmable Josephson voltage standards (PJVSs) in combination with fast switchable DC current sources have opened up new applications in the field of low-frequency AC metrology. The growing interest in output voltages of up to  $\pm 10$ V initiated efforts by several National Metrological Institutes to realize 10 V PJVSs. Presently, only 10 V PJVSs from PTB based on SINIS junctions have been successfully incorporated into existing setups for AC metrology. However, the fabrication of 10 V SINIS arrays that are driven at 70 GHz suffers from very low yield. The recent technological progress made at NIST enabled the drop-in replacement of the low-yield SINIS arrays by more robust SNS arrays. The N-material is an amorphous Nbx Si1-x alloy near the metal-insulator transition and is deposited by co-sputtering. For the first time, fully operational 1 V and 10 V PJVSs with SNS junctions that are suitable for a 70 GHz drive have been fabricated and tested. This work was done in close cooperation between NIST and PTB.

Index Terms—AC Josephson voltage standard, Josephson arrays, programmable Josephson voltage standard, SINIS junction, SNS junction.

### I. INTRODUCTION

THE STATE of the art in AC voltage metrology is based on two fundamental achievements of recent Josephson technology: the Programmable Josephson Voltage Standard (PJVS) [1] operated by sinusoidal microwaves and the Josephson Arbitrary Waveform Synthesizer (JAWS) [2], which is driven by ultra-short current pulses. According to the fundamental equation for Josephson voltage metrology,

$$U(t) = nM(t)f/K_{J-90},$$

(1)

the PJVS systems exploit this equation by rapidly programming the voltage U(t) by changing the junction number M by biasing different sub-arrays with different numbers of junctions.  $K_{\rm J}$ –90 is the Josephson constant ( $K_{\rm J}$ –90 = 483 597.9 GHz/V), n denotes the order of Shapiro steps (typically using the three voltage states n=0, and  $\pm 1$ ) and f the microwave frequency. Despite the use of fast switchable DC bias sources, the unavoidable

Manuscript received August 18, 2008. First published June 30, 2009; current version published July 10, 2009.

Digital Object Identifier 10.1109/TASC.2009.2017911

transients during the change of voltage states restrict the possible applications of the PJVS to DC and low frequencies, less than 1 kHz. However, in contrast to pulse-driven arrays (JAWS), which allow synthesis of fundamentally accurate AC voltages, only the PJVS can be operated at higher voltages of up to 10 V with an acceptable technological effort. Such 10 V PJVS systems enable new applications in the field of low-frequency AC metrology, especially when the time-varying Josephson voltage is used as a reference to measure a waveform differentially [3]. In this paper, we focus on the use of a junction-barrier material near the metal-insulator transition that could help to overcome fabrication yield limitations for PJVS circuits fabricated by the SINIS junction technology at PTB (S = superconductor, I =insulator, N = normal metal). We describe how two National Metrology Institutes, NIST in the U.S.A. and PTB in Germany, cooperate to realize the first 1 V and 10 V PJVS with a  $Nb_xSi_{1-x}$  barrier that can be driven at 70 GHz.

## II. REQUIREMENTS ON JOSEPHSON JUNCTIONS SUITABLE FOR PJVS ARRAYS

In order to generate stable and rapidly programmable DC voltages, Hamilton  $\it et al.$  proposed and developed the first PJVS [1]: an array subdivided into smaller array segments following a binary (or later ternary) sequence for the number of junctions. This array sequence allows, in combination with individual and fast switchable DC bias sources, the rapid generation of quantized voltages. The combined total step number  $\it nM$  for the whole array can thus be set to any integer value between  $\it -M$  and  $\it +M$ . Fast changes in the output voltage are possible only if there are single-valued Shapiro steps in the current-voltage characteristic (IVC) under microwave irradiation. This condition requires the use of overdamped Josephson junctions that display an IVC with negligible hysteresis.

For their first approach, Hamilton and co-workers used externally shunted SIS junctions based on the reliable Nb-Al technology at NIST. However, due to the external shunt resistance and its large parasitic inductance (which creates microwave-design problems and additional fabrication difficulties), the implementation of SIS junctions in a PJVS was abandoned shortly afterwards. Some years later, Seppä  $et\ al.$  from VTT, Finland, took up the original idea and developed a 1 V PJVS with externally shunted SIS junctions driven with microwaves at around 75 GHz [4]. The small current margins obtained ( $\approx 150\ \mu\text{A}),$  made AC applications difficult. All of these disadvantages can be avoided by the use of internally shunted Josephson junctions such as SINIS or SNS.

When NIST first implemented SNS junctions [5], the low resistivity of the junction barrier required a "low" frequency drive

F. Mueller, R. Behr, T. Weimann and L. Palafox are with the Physikalisch-Technische Bundesanstalt (PTB), 38116 Braunschweig, Germany (e-mail: franz.mueller@ptb.de).

D. Olaya, P. D. Dresselhaus and S. P. Benz are with the National Institute of Standard and Technology (NIST), Boulder, CO 80305 USA (e-mail: samuel. benz@nist.gov).

around 15 GHz. At that time, the commonly used and technologically available barrier materials for SNS junctions such as AuPd, TiHf or later on  ${\rm TiN_x}$  resulted in  $I_{\rm c}R_{\rm n}$  products ( $I_{\rm c}$ : critical current,  $R_{\rm n}$ : normal resistance) of typically 10  $\mu{\rm V}$  to 40  $\mu{\rm V}$  when deposited to reasonable thicknesses to make micrometer-sized junctions with practical current densities. NIST and AIST succeeded in the fabrication of such programmable circuits [6], [7], but the large number of junctions operating at 16 GHz required to reach 10 V remains a challenge for this junction technology. In spite of all the technological problems, the junction uniformity demonstrated by the planar SNS fabrication process was the motivation to start the present collaboration on SNS junctions and circuits designed to operate at 70 GHz that would require considerably fewer junctions.

PTB followed an alternative route and explored SINIS junctions for PJVSs [8]. These junctions use the same 70 GHz microwave drive that is the typical bias frequency for conventional SIS Josephson voltage standards (JVSs), which are commonly used by the voltage-metrology community. This is possible because the  $I_{\rm c}R_{\rm n}$  product of this junction type with double insulating barriers can easily be tuned over a large frequency range. Therefore the necessary number of junctions is 4 to 5 times fewer than in a PJVS driven at 15 GHz, and the entire microwave distribution network can be fabricated on-chip. Moreover, except for some minor modifications, the array fabrication is based on the reliable Nb-Al standard technology for conventional JVSs [9].

Today, SINIS 1 V PJVSs displaying current margins larger than 1 mA, a value that provides enough noise immunity for AC applications, are fabricated routinely at PTB with an acceptable yield of about 30%. Programmable 10 V SINIS junction arrays with 69 632 Josephson junctions divided into 22 segments (16 bits) and current margins larger than 600  $\mu$ A have also been produced in small numbers [10] and their suitability for numerous metrological AC applications has been proven [11]–[13]. Unfortunately, the fabrication yield of these 10 V PJVSs is quite low (about 5%). However, the demand for such systems is continuously increasing. For that reason, PTB is seeking new materials and evaluating their suitability for a programmable SNS version that would enable higher fabrication yield and that can be used as a drop-in replacement for existing 70 GHz SIS or SINIS systems.

## III. COMPARISON OF SINIS AND SNS ARRAYS AND THEIR IMPACT ON TECHNOLOGY AND DESIGN

### A. Fundamental Junction Properties

Both SNS and SINIS Josephson junctions belong to a class of weak links that are dominated by the proximity effect [14]. The main difference is that SINIS junctions have well-defined (engineered) interfaces between the superconducting electrodes and the sandwiched normal metal N. These well-defined interfaces are extremely thin (1 nm to 2 nm thick) AlO $_{\rm x}$  barriers. Fortunately, the necessary increase of the transparency of these barriers, up to a level dominated by pinholes, does not lead to a large spread of electrical parameters due to the averaging of the pinhole contributions from the two interfaces [14]. Nevertheless, achieving practical run-to-run reproducibility is a challenging

task because the required oxygen exposure, product of pressure and oxidation time, is extremely low (less than 25  $Pa \cdot s$ ). The main problem in the fabrication of SINIS arrays at PTB seems to be plasma-induced damage during wafer processing. We believe that locally enhanced voltages during the plasma processes create large pinholes (larger than the coherence length!) that result in additional current contributions. Similar effects have also been found for SIS junctions with high current densities [15]. This kind of damage is visible by singular increased critical currents, observed for about 0.01% of the junctions in an array. Depending on their exact  $I_c$ , the effected junctions remain either superconductive; i.e., they provide no contribution to the step voltage ("missing junctions") or they contribute in a way that the step is no longer usable (too small or sloped). Among all possible failure sources in the very complex SINIS fabrication process, the excessive critical currents are the main reason for the low yield of 10 V PJVSs.

The technology for classical SNS junctions is much simpler and more robust, because only the thickness of a given N-layer determines both  $I_cR_n$  and the current density  $j_c$  under the condition of clean interfaces and negligible interdiffusion. Until recently, most applications had to take into consideration a low  $I_{\rm c}R_{\rm n}$  (10  $\mu{\rm V}$  to 40  $\mu{\rm V}$ ) and at the same time a large  $j_{\rm c}$  (80 kA/cm<sup>2</sup> to 200 kA/cm<sup>2</sup>) [5], [6]. Recent progress made in junction technology based on N-materials near the metal-insulator (M-I) transition paved the way to "high"-frequency applications above 70 GHz [16], [17]. Today, NIST is able to fabricate Nb junctions with amorphous  $Nb_xSi_{1-x}$ -barriers that can be tuned by changing the Nb content of the barrier from nearly SIS (small x) to SNS behavior (x > 0.12) [18]. For the first time, programmable voltage standards able to operate either at "low" or "high" frequencies and fabricated by practically the same technology but with differently tuned barriers are a realistic goal.

## B. Junction and Circuit Design for 70 GHz

Our first approach assumes nearly identical microwave designs for SNS and SINIS circuits, except for the junction area  $(l \cdot w)$  and the stripline impedance  $Z_0$ . Details have been described elsewhere and are summarized in Table I [10]. Similarly, the design of a single SNS junction  $(N = Nb_xSi_{1-x})$  embedded in a stripline follows the principles valid for SINIS junctions. That means, in terms of the RSJ model, according to Kautz [19]:

- Negligible hysteresis, i.e.,  $\beta_{\rm c} = I_{\rm c}/I_{\rm R} \approx 1$  (McCumber parameter,  $I_{\rm R} = {\rm switching back}$  current of the IVC).

- A normalized frequency  $\Omega = f/f_c \approx 1$ , with  $f_c = hf/(2eI_cR_n)$ , delivering an optimum  $I_cR_n = 145 \ \mu\text{V}$ .

- A critical current  $I_{\rm c} \leq 3~{\rm mA}$  to limit the RF power per stripline:  $P_{\rm rf} = Z_0 I_{\rm rf}^2/2$ , to  $\approx 0.3~{\rm mW}$  ( $I_{\rm rf} \approx 2I_{\rm c}$ : RF current amplitude and  $Z_0 = 16~\Omega$ ). Under similar conditions, both 1 V (64 parallel microwave stripline branches) and 10 V (128 branches) SINIS circuits ( $Z_0 = 12~\Omega$  can be driven by Gunn diodes with a maximum output power of 100 mW.

- Preliminary investigations at NIST on junctions with high-resistivity  ${\rm Nb_xSi_{1-x}}$ -barriers delivered a current density of  $j_{\rm c}\approx 2000~{\rm A/cm}^2$  for the targeted  $I_{\rm c}R_{\rm n}=150~\mu{\rm V}$ . With this value, the dimensions of a single junctions were fixed to  $l=6~\mu{\rm m}$  (length) and  $w=20~\mu{\rm m}$  (width). Both are less

TABLE I

DESIGN PARAMETERS FOR BINARY DIVIDED SINIS AND SNS CIRCUITS

| Parameter               | Circuit | SINIS  | SNS (N=Nb <sub>x</sub> Si <sub>1-x</sub> ) |

|-------------------------|---------|--------|--------------------------------------------|

| Number of junctions     | 1 V     | 8 192  | 8 192                                      |

|                         | 10 V    | 69 632 | 69 632                                     |

| Striplines connected in | 1 V     | 64     | 64                                         |

| parallel                | 10 V    | 128    | 128                                        |

| Number of junctions     | 1 V     | 128    | 128                                        |

| per stripline           | 10 V    | 136562 | 136—582*                                   |

| Stripline impedance     |         | 12     | 16                                         |

| $[\Omega]$              |         | 12     | 16                                         |

| Junction length [µm]    |         | 12     | 6                                          |

| Junction width [µm]     |         | 30     | 20                                         |

| Current density         |         | 750    | 2500                                       |

| [A/cm <sup>2</sup> ]    |         | 730    | 2300                                       |

| Critical current [mA]   |         | 3.5    | 3                                          |

| Normal resistance       |         | 41     | 48                                         |

| $[m\Omega]$             |         | +1     | 46                                         |

<sup>\*</sup>in contrast to SINIS, the number of junctions in some striplines is slightly different.

than 4 times the Josephson penetration depth  $\lambda_{\rm J}=8.2~\mu{\rm m}$ , so that we can assume a nearly homogeneous current distribution, i.e.,  $I_{\rm c}=j_{\rm c}lw$  [20].

The maximum number of SNS junctions (Table I) that can be embedded into one of the parallel-driven striplines, in order to maintain an approximately constant microwave current, is one of the most important design parameters for the microwave circuit. This number is determined by the microwave attenuation of the stripline and is due mainly to losses from the embedded junctions. The damping per junction  $\alpha_J$  can be estimated for a passive stripline ( $I_{\rm dc}=0$ ), according to Kautz [21], as

$$\alpha_{\rm J} = 10 \log_{10} \left[ 1 - 3/(4\pi^2 f^2 R_{\rm n} Z_0 C^2) \right].$$

(2)

With the above design parameters and an effective junction capacitance  $C=47~\mathrm{pF}$  deduced from  $\beta_c=1$ , this formula delivers  $\alpha_\mathrm{J}=0.04~\mathrm{dB}$  per junction. This value is comparable to the measured microwave damping of SINIS arrays and would never allow the integration of a large number of junctions in a single stripline [22]. However from our earlier investigations with SINIS arrays, it is known that in active striplines ( $I_\mathrm{dc}>I_\mathrm{c}$ ) self-oscillation coupling effects between the junctions partly compensate the increased attenuation [22]. This effect is well described by a virtual model for our SINIS circuits by Kim *et al.* [23].

Nevertheless, for our PJVS designs, we had to take into consideration that all unbiased array segments can present a non-negligible microwave attenuation. For that reason, the first stripline (on one side of the circuit) has all the smallest array sections (bits: 0–6) and is the most critical in regard to microwave attenuation. Thus, the segments with 64 junctions for the 1 V circuit (or with 68 junctions for the 10 V circuit) combined with the "largest" array striplines (128 or 582 JJs), which are always biased collectively, determine the attainable current margins of the microwave-induced steps. The number of striplines connected in parallel, 64 for the 1 V design (8 192 total JJs) and 128 for the 10 V design (69 632 total JJs) is a compromise between tolerable damping (including self-excitation) and available microwave power (less than 50 mW at

antenna) at 70 GHz. The distribution of all junctions over the striplines is determined by an exact (1 V) or an approximated (10 V) binary sequence for the number of junctions in the array segments.

Besides the primary design goal of maintaining nearly the same microwave power for all junctions, the circuit area containing all junctions should be concentrated as much as possible, to minimize the parameter spread. For that reason, DC connections to the array segments have been restricted to the ends of the striplines and to one of the two outermost striplines. All these practical considerations and a number of experimental investigations on test arrays resulted in a "homogenous" 1 V design with 128 junctions in each stripline and an "inhomogenous" 10 V design. The 69 632 junctions are subdivided into 22 segments with different numbers of junctions per stripline: 4 striplines with 136 JJs, 2 striplines with 272 JJs, and 122 striplines with junction numbers between 544 and 582. All striplines are extended beyond the array length with superconducting wires in order to reach the microwave termination and to match all the lengths.

#### IV. FABRICATION PROCESS

#### A. Trilayer Deposition at NIST

Trilayer films are grown on SEMI standard 76.2 mm Si wafers with 150 nm of dry thermal oxide to passivate the bare wafer. The wafer is loaded into a load-locked vacuum chamber where an initial rf plasma is used to clean the surface of contamination. An initial layer of 245 nm of Nb is grown as a base electrode, followed by an additional rf plasma to enhance the planarity of the base electrode. After waiting 3 min for the wafer and guns to reach thermal equilibrium, the Nb-Si is co-sputtered from the Nb sputter gun (under the same conditions as the electrode Nb) and a p-doped Si sputter target. Finally, the Nb top-electrode of 200 nm thickness is deposited.

Because the exact Nb content in a film is not measured, the best characterization of the Nb content is the power from the Nb sputter gun, assuming a fixed power on the Si sputter gun. For the trilayers in this study, a power of 17 W was used on the Nb gun and 200 W on the Si gun giving a Nb content of  $\sim\!8\%$ . As the sputter targets age, this composition slightly changes. The same process may be used to fabricate stacks of junctions by inserting a middle Nb electrode and additional  $\mathrm{Nb_xSi_{1-x}}$  layer before the top-electrode growth.

## B. Trilayer Patterning at PTB

In contrast to SINIS arrays [9], SNS circuits were fabricated with a conventional self-aligning process that is very similar to the fundamental SNEP process first developed by Gurvich *et al.* [24]. The main difference is the amorphous  $Nb_xSi_{1-x}$  barrier instead of  $AlO_x$ . With the exception of the groundplane and the load resistor, all metallic and insulating layers were patterned using e-beam lithography.

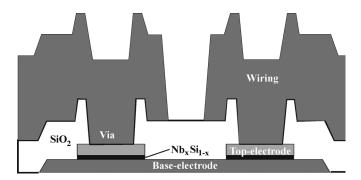

The trilayer patterning starts with the junction definition (Fig. 1). This is done by ICP (Inductive Coupled Plasma) etching of the Nb top electrode (200 nm thick) and the NbSi barrier (10 nm) with a mixture of  $SF_6$  and  $C_4F_8$ . As there is no natural etch-stop, a laser endpoint-detection system indicates

Fig. 1. Cross-section of all layers of the DC circuit.

when the interfaces between the NbSi-barrier and the Nb of the top and bottom electrode are successively cleared. In a second fabrication step, the base electrodes (~ bottom Nb, 245 nm thick) are reactively ion-etched (RIE-parallel plate reactor) with  $CF_4$  and  $O_2$ . To insulate the base electrodes from the wiring, SiO<sub>2</sub> is deposited to a thickness of 350 nm using a PECVD (Plasma Enhanced Chemical Vapor Deposition) system with an ICP-source. Rectangular shaped vias (3  $\mu$ m by 17  $\mu$ m) to the top electrodes are etched through the oxide by ICP-etching with  $CHF_3$  and  $O_2$ . Prior to the deposition of the 500 nm thick Nb wiring, an in-situ cleaning process by rf etching enables superconducting contact ( $I_{max} > 70 \text{ mA}$ ) between the top electrode and the wiring. The patterning process of the wiring level by RIE etching in  $CF_4 + O_2$  completes the DC circuit. Fig. 1 shows a cross-sectional view of all layers in the DC circuit. The microwave circuit is completed with a 1.5  $\mu m$  thick PECVD SiO<sub>2</sub> insulating layer, a superconducting ground-plane (250 nm Nb) and a load-resistance built by a normal metal plane from AuPd (200 nm thick). The microwave layers on top of the DC circuit are patterned by optical-contact lithography. In the final fabrication step, the thick SiO<sub>2</sub> covering the DC pads, is removed by wet etching.

## V. EXPERIMENTAL RESULTS AND DISCUSSION

During a first stage of the PTB—NIST collaboration, the focus was on the development of a reliable fabrication process and on relevant electrical properties, such as the parameter-spread of the SNS junction arrays with NbSi-barriers tuned for 70 GHz. In the initial search for the right deposition recipe, 5 trilayer wafers with slightly varied barriers were deposited as described above and patterned into 1 V circuits. Only one of these (trilayer #1 in Table II) was close to the targeted electrical parameters. The other processed wafers had values for  $I_{\rm c}$  and  $I_{\rm c}R_{\rm n}$  that were too large and showed various chaotic behaviors under microwave irradiation. Most of the 21 circuits were evaluated from the wafer with trilayer #1. From these measurements we could deduce a spread for  $I_{\rm c}$  and  $I_{\rm c}R_{\rm n}$  across the wafer of  $\pm 25\%$  and  $\pm 12\%$ , respectively. The evaluation of the other wafers has not been completed.

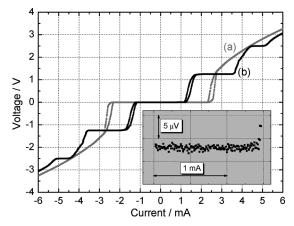

Fig. 2 presents a typical IVC of a 1 V circuit from trilayer #1 without (a) and with (b) microwave bias. The first Shapiro step extends, as demonstrated by the inset picture, over a current range of approximately 1.4 mA, and the hysteresis does not influence the low-current edge of the step. It seems that the

TABLE II ELECTRICAL PARAMETERS OF TRILAYERS USED FOR 1 V AND 10 V PJVSS

| trilayer#    | I <sub>c</sub> <sup>av</sup> (mA) | $I_{c}R_{n}^{av}(\mu V)$ |  |

|--------------|-----------------------------------|--------------------------|--|

| #1 (only 1V) | 2.3                               | 170                      |  |

| #2           | 0.75                              | 200                      |  |

| #3           | 3                                 | 150                      |  |

| #4           | 2.5                               | 125                      |  |

$I_{\rm c}^{\rm av}$ ,  $I_{\rm c}R_{\rm n}^{\rm av}$ : averaged values,  $R_{\rm n}$  determined at  $2\,I_{\rm c}$ . All trilayer barriers were nominally 11 nm thick. Trilayer #2 was grown with an aged Nb target, thus the Nb content is likely to be less than the nominal 8%.

Fig. 2. IVC of a 1 V-PJVS with 8 192 SNS junctions, (a) without microwaves, (b) with microwaves at 73.668 GHz and 20 mW at antenna. The inset picture shows the first Shapiro step with high resolution. Junction parameters:  $I_{\rm c}=2.35~{\rm mA},\,I_{\rm c}R_{\rm n}=160~\mu{\rm V}$  (at  $2I_{\rm c}$ ).

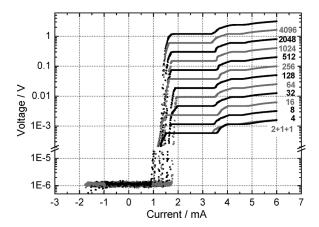

$I_{\rm c}R_{\rm n}$  product of 160  $\mu{\rm V}$ , measured at  $2I_{\rm c}$  of the bending IVC, presents approximately a limit for non-hysteretic higher-order steps. Measurements on circuits from the same wafer demonstrated that a further increase of  $I_{\rm c}R_{\rm n}$  beyond this limit renders the constant-voltage steps increasingly hysteretic. The undesirable hysteretic parts at one or both ends of a step can be removed by applying a sufficiently large microwave power. However, in such cases the optimum operating condition for PJVSs of "equal step widths" [19] for the steps n = 0 and  $n = \pm 1$  is no longer fulfilled. In order to demonstrate that the 1 V PJVS is fully operational, the IVCs under microwave irradiation of all array segments have been recorded. Fig. 3 shows that all current margins are approximately 1.4 mA. This value gives sufficient noise immunity for most AC applications. The equal step-width condition serves as a figure of merit for the microwave design and the junction uniformity. For the fabricated 1 V PJVSs with SNS junctions, we have measured a value of approximately 0.6  $I_{\rm c}$ . Equally good results have been obtained with SINIS circuits [10].

Encouraged by the good performance of the 1 V PJVSs, five more trilayers were grown and patterned into 10 V circuits using the design described previously. Due to a necessary optimization of some critical fabrication steps, including e-beam lithography, only the trilayers #2, #3 and #4 delivered 10 V circuits that could be evaluated. Despite the parameter spread evaluated previously for trilayer #1, and considering the "large" area covered by the junctions in the 10 V design (7.5 mm by 9)

Fig. 3. IVC of a complete 1 V array and of all segments under microwave irradiation at 70.5 GHz and 15 mW at antenna. The number of junctions in each segment is indicated to the right of the corresponding curve and increases from bottom to top in a binary sequence.

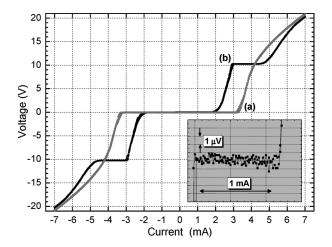

Fig. 4. IVC of a 10 V PJVS with 69 632 SNS junctions, (a) without microwaves, (b) with microwaves at 71.28 GHz and 50 mW at antenna. The inset shows the 10 V step with high resolution. Junction parameters:  $I_{\rm c}=3.05~{\rm mA}$ ,  $I_{\rm c}R_{\rm n}=150~\mu{\rm V}$  (at  $2I_{\rm c}$ ).

mm), the measurements on 10 V arrays delivered surprisingly good results. In particular, the circuits patterned from trilayer #3, with values for  $I_{\rm c}$  and  $I_{\rm c}R_{\rm n}$  nearly equal to the design values, demonstrated excellent performance. The IVC with microwaves (shown in Fig. 4(b)) demonstrates current margins for the 10 V step of approximately 1.2 mA. Steps as large as 1.4 mA were obtained by optimizing the microwave signal. These current margins are nearly two times larger than those obtained for 10 V PJVSs with SINIS junctions. Moreover, a precision measurement of the step voltage (see inset of Fig. 4) reveals that all of the 69 632 junctions are phase-locked to the external microwave at 71.28 GHz. All 10 V SINIS arrays fabricated to date have had at least one "missing junction".

One of the fabricated 10 V SNS arrays (from trilayer #2) was used to perform a comparison with the 10 V SIS JVS of the PTB. This comparison showed good agreement at the 10 V level with a difference of  $\Delta U_{\rm SIS-SNS} = 0.04~\rm nV \pm 0.41~\rm nV$  (type A uncertainty).

Other remarkable features of the IVC are the nonhysteretic IVC without microwaves (Fig. 4(a)) and the smooth (smeared)

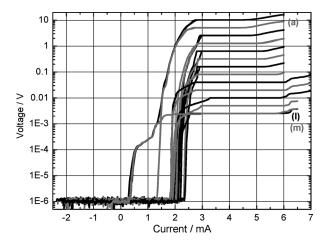

Fig. 5. IVC of a complete 10 V array and of different array segments under microwave irradiation at 71.28 GHz and 50 mW at antenna. For clarity, the smaller segments were grouped for curve (m) The number of Josephson junctions in each segment decreases alphabetically from top to bottom: (a) 34 816, (b) 17 408, (c) 8 704, (d) 4 352, (e) 2 176, (f) 1 088, (g) 544, (h) 272, (i) 136, (j) 68, (k) 34, (l) 17, and (m) 1+1+2+4+8=17. The IVC for the complete array is dominated by (m) at low currents, then (a). The width of the step is limited by the overlap between (a) and (j).

transition at the ends of the microwave-induced n = 0 step. The reason for the latter phenomenon is visible in Fig. 5, which shows the IVCs of the whole 10 V PJVS and of nearly all array segments of the 10 V PJVS under microwave irradiation. Clearly, the first 17 junctions, which are the sum of the smallest bits  $(3 \times \text{bit } 0 + \text{bit } 1 + \text{bit } 2 + \text{bit } 3)$ , display a step width for n=0 of only 500  $\mu$ A, whereas the "large" bits are close to the target-value of "equal step widths". We believe that the reason for this behavior, which was not observed on any SINIS circuits, is the special design situation of the outer stripline of the 10 V array with many narrowly spaced DC connections to the first array segments. These connections (without filters) can act as antennae for parasitic microwaves, so that the first junctions are overdriven and, due to the special Bessel-function behavior of the Shapiro steps [16], [17], rapidly reduces the step width for n = 0. Nevertheless, the obtained step width of at least 0.4  $I_c$  for the first Shapiro step in all segments is an excellent figure of merit for our 10 V design.

## VI. CONCLUSION

The fabricated arrays with co-sputtered  $\mathrm{Nb_xSi_{1-x}}$  barriers can be used as drop-in replacements for SINIS arrays in existing 1 V and 10 V PJVS systems operated at 70 GHz. 10 V SNS arrays show an improved performance as compared to 10 V SINIS arrays, having better yield and larger current widths of the steps. The SNS junction technology has better yield, most likely because plasma process-induced damage of the barrier is eliminated. Further improvements of the 10 V design should focus on the first stripline with the smallest bits in order to achieve nearly equal stepwidths for all array segments.

## ACKNOWLEDGMENT

The authors thank R. Wendisch, B. Egeling, R. Harke, and P. Hinze for technical support, I. Krasnopolin and J. Lee for their

assistance with some of the measurements, and O. Kieler and J. Kohlmann for helpful discussions.

#### REFERENCES

- C. A. Hamilton, C. J. Burroughs, and R. L. Kautz, "Josephson D/A converter with fundamental accuracy," *IEEE Trans. Instrum. Meas.*, vol. 44, pp. 223–225, Apr. 1995.

- [2] S. P. Benz and C. A. Hamilton, "A pulse-driven programmable Josephson voltage standard," *Appl. Phys. Lett.*, vol. 68, pp. 3171–3173, May 1996.

- [3] R. Behr, L. Palafox, G. Ramm, H. Moser, and J. Melcher, "Direct comparison of Josephson waveforms using an AC quantum voltmeter," *IEEE Trans. Instrum. Meas.*, vol. 56, no. 2, pp. 235–238, Apr. 2007.

- [4] J. Hassel, H. Seppä, L. Grönberg, and I. Suni, "Optimization of a Josephson voltage array based on frequency dependently damped superconductor-insulator-superconductor junctions," *Rev. Sci. Instr.*, vol. 74, pp. 3510–3515, July 2003.

- [5] S. P. Benz, "Superconductor-normal-superconductor junctions for programmable voltage standards," *Appl. Phys. Lett.*, vol. 76, pp. 2714–2716, Oct. 1995.

- [6] S. P. Benz, C. A. Hamilton, C. J. Burroughs, T. E. Harvey, and L. A. Christian, "Stable 1-volt programmable voltage standard," *Appl. Phys. Lett.*, vol. 71, pp. 1866–1868, Sept. 1997.

- [7] H. Yamamori, M. Ishizaki, A. Shoji, P. D. Dresselhaus, and S. P. Benz, "10 V programmable Josephson voltage standard circuits using NbN/TiN<sub>x</sub>/NbN/TiN<sub>x</sub>/NbN double junction stacks," *Appl. Phys. Lett.*, vol. 88, no. 4, pp. 1–3, Jan. 2006, 042503.

- [8] H. Schulze, R. Behr, F. Müller, and J. Niemeyer, "Nb/Al/AlOx/Al/Nb Josephson junctions for programmable voltage standards," *Appl. Phys. Lett.*, vol. 73, pp. 996–998, Aug. 1998.

- [9] F. Müller, H. Schulze, R. Behr, J. Kohlmann, and J. Niemeyer, "The Nb-Al technology at PTB-a common base for different types of Josephson voltage standards," *Physica C*, vol. 354, pp. 66–70, 2001.

- [10] F. Müller, R. Behr, L. Palafox, J. Kohlmann, R. Wendisch, and I. Krasnopolin, "Improved 10 V SINIS series arrays for applications in AC voltage metrology," *IEEE Trans. Appl. Supercond.*, vol. 17, pp. 649–652, June 2007.

- [11] L. Palafox, R. Behr, W. G. Kuerten, Ihlenfeld, F. Müller, E. Mohns, M. Seckelmann, and F. Ahlers, "The Josephson effect based primary ac power standard at PTB: Progress report," *IEEE Trans. Instrum. Meas.*, 2008, submitted for publication.

- [12] R. Iuzzolino, L. Palafox, W. G. Kuerten, Ihlenfeld, E. Mohns, and C. Brendel, "A sampling system based on  $\Sigma-\Delta$  analog-to-digital converters," *IEEE Trans. Instrum. Meas.*, 2008, submitted for publication.

- [13] S. Djordjevic, O. Séron, S. Solve, and R. Chayramy, "Direct comparison between a programmable and a conventional Josephson voltage standard at the level of 10 V," *Metrologia*, vol. 45, pp. 429–435, Aug. 2008

- [14] M. Y. Kupriyanov, A. Brinkmann, A. A. Golubov, M. Siegel, and H. Rogalla, "Double-barrier Josephson structures as the novel elements for superconducting large-scale integrated circuits," *Physica C*, vol. 326–327, pp. 16–45, 1999.

- [15] S. K. Tolpygo, D. Amparo, A. Kirichenko, and D. Yohannes, "Plasma process-induced damage to Josephson tunnel junctions in superconducting integrated circuits," *Supercond. Sci. Technol.*, vol. 20, pp. S341–S349, 2007.

- [16] B. Baek, P. D. Dresselhaus, and S. P. Benz, "Co-sputtered amorphous  $\mathrm{Nb_{x}Si_{1-x}}$  barriers for Josephson-junction circuits," *IEEE Trans. Appl. Supercond.*, vol. 16, pp. 1966–1970, Dec. 2006.

- [17] L. Yu, R. Andikota, R. K. Singh, L. Gu, D. J. Smith, X. Meng, X. Zeng, T. Van Duzer, J. M. Rowell, and N. Newman, "Internally shunted Josephson junctions with barriers tuned near the metal-insulator transition for RSFQ logic applications," *Supercond. Sci. Technol.*, vol. 19, pp. 719–731, 2006.

- [18] D. Olaya, B. Baek, P. D. Dresselhaus, and S. P. Benz, "High-speed Nb/Nb-Si/Nb Josephson junctions for superconductive digital electronics," *IEEE Trans. Appl. Supercond.*, submitted for publication.

- [19] R. L. Kautz, "Quasipotential and the stability of phase lock in nonhysteretic Josephson junctions," *J. Appl. Phys.*, vol. 76, pp. 5538–5544, Nov. 1994.

- [20] R. L. Kautz, "Shapiro steps in large-area metallic-barrier Josephson junctions," J. Appl. Phys., vol. 78, pp. 5811–5819, Nov. 1996.

- [21] R. L. Kautz, "Design and operation of series array Josephson voltage standards," in *Metrologie at the Frontier of Physics and Technology*, L. Crovini and T. J. Quinn, Eds. Amsterdam, The Netherlands: North-Holland, 1992, pp. 259–296.

- [22] R. Behr, H. Schulze, F. Müller, J. Kohlmann, I. Krasnopolin, and J. Niemeyer, "Microwave coupling of SINIS junctions in a programmable Josephson voltage standard," in *Proc. ISEC'99, Ext. Abstr.*, June 1999, pp. 128–130.

- [23] K.-T. Kim, M.-S. Kim, Y. Chong, and J. Niemeyer, "Simulations of collective synchronization in Josephson junction arrays," *Appl. Phys. Lett.*, vol. 88, no. 6, pp. 062501:1–062501:3, Febr. 2006.

- [24] M. Gurvitch, W. A. Washington, and H. A. Huggins, "High quality refractory Josephson tunnel junctions utilizing thin aluminium layers," *Appl. Phys. Lett.*, vol. 42, pp. 472–474, 1983.